Laptop-Motherboards konzentrieren Desktop-Klasse-Rechenleistung auf Platinen, die ungefähr 250 mm × 200 mm messen – oft kleiner für Ultrabooks. Diese Komprimierung erfordert sorgfältige Aufmerksamkeit auf die High-Speed-Signalintegrität für DDR5-Speicherschnittstellen, eine robuste Stromversorgung für Prozessoren, die 45-65 W ziehen (Gaming-Laptops überschreiten 150 W kombinierte CPU+GPU), Wärmemanagement innerhalb der Gehäusegrenzen und eine Fertigungsqualität, die Zuverlässigkeit über Jahre von thermischen Zyklen und mechanischer Beanspruchung gewährleistet.

Dieser Leitfaden adressiert die PCB-spezifischen Herausforderungen im Laptop-Design: Lagenaufbau-Optimierung für Signalintegrität und Stromversorgung, DDR5- und PCIe-Routing-Beschränkungen, Design des Stromversorgungsnetzwerks für moderne Prozessoren, thermische Strategien, die innerhalb von Notebook-Formfaktoren funktionieren, und die Fertigungsfähigkeiten, die für eine konsistente Produktionsqualität erforderlich sind.

In diesem Leitfaden

- Lagenaufbau-Design für High-Speed und Power-Integrität

- Anforderungen an das Routing von DDR5-Speicherschnittstellen

- Design des CPU- und GPU-Stromversorgungsnetzwerks

- Wärmemanagement durch PCB-Design

- Fertigungsüberlegungen für Laptop-Motherboards

- Zuverlässigkeitsprüfung und Qualitätsanforderungen

Lagenaufbau-Design für High-Speed und Power-Integrität

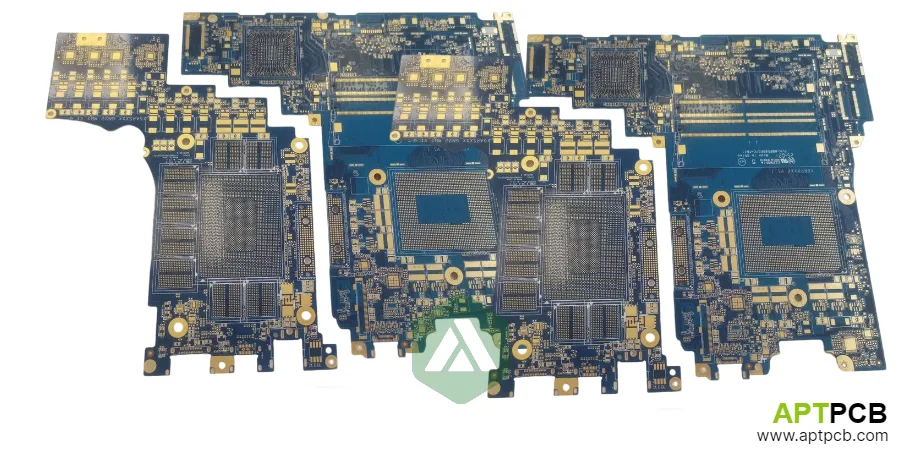

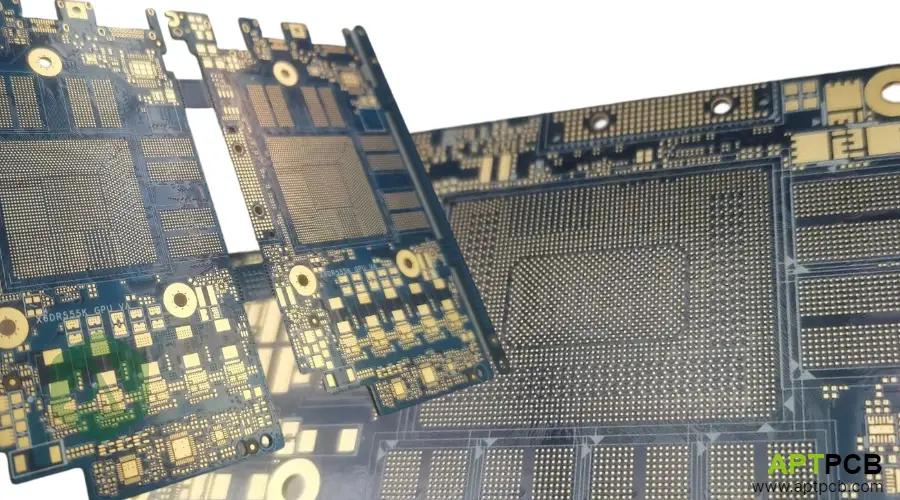

Moderne Laptop-Motherboards erfordern typischerweise 10 bis 14 Lagen. Im Gegensatz zu Server-Boards, die die Dicke auf über 3 mm erhöhen können, um mehr Lagen unterzubringen, sind Laptop-PCBs auf 1,0 mm bis 1,2 mm Gesamtdicke beschränkt, um in schlanke Gehäuse (z-Höhe) zu passen. Diese Einschränkung zwingt Entwickler zur Verwendung fortschrittlicher High-Density-Interconnect (HDI)-Strukturen und ultradünner Dielektrika.

Der Lagenaufbau (Stackup) muss konkurrierende Anforderungen ausbalancieren: Die Impedanzkontrolle für PCIe Gen 4/5 und USB4 erfordert spezifische Dielektrikumsdicken, während die PDN-Optimierung (Power Delivery Network) einen minimalen Abstand zwischen Stromversorgungs- und Masselagen verlangt, um die Kapazität in der Platine zu maximieren.

HDI-Strukturen in Laptop-PCBs

Laptop-Designs verlassen sich zunehmend auf HDI, um große Pin-Count-BGAs (wie Intel Core- oder AMD Ryzen-Prozessoren) zu entflechten und das Routing auf begrenztem Platz zu optimieren.

- Any-Layer HDI (ELIC): Premium-Ultrabooks nutzen oft Every Layer Interconnect-Aufbauten, die Microvias zwischen beliebigen benachbarten Lagen ermöglichen. Dies maximiert die Routing-Dichte und minimiert die Platinengröße, erhöht jedoch die Fertigungskosten erheblich.

- 1+N+1 und 2+N+2 Strukturen: Mainstream-Laptops verwenden in der Regel gestaffelte oder gestapelte Microvias auf den äußeren Lagen mit durchgehenden Vias (Plated Through-Hole, PTH) im Kern. Eine 10-lagige 2+6+2-Konstruktion bietet ausreichend Fanout für die meisten Standardprozessoren und Speicher-Chips.

- Via-in-Pad (VIPPO): Unverzichtbar für feine BGA-Pitches (0,4 mm bis 0,5 mm) in Prozessoren und Chipsätzen. Die Vias müssen mit Epoxidharz gefüllt und mit Kupfer überzogen (capped) sein, um zu verhindern, dass Lot während der Montage in das Loch fließt.

Materialauswahl für Lagenaufbau

Die Wahl des Materials für Laptop-PCBs erfordert ein Gleichgewicht zwischen elektrischer Leistung, thermischer Stabilität und Kosten. Bei der Auswahl von Leiterplatten-Basismaterialien für Laptop-Anwendungen gehören zu den wichtigsten Überlegungen:

- Mittel-Verlust (Mid-Loss) vs. Niedrig-Verlust (Low-Loss): Während Standard-FR4 für Altsysteme ausreichte, erfordern PCIe Gen 4/5 und Thunderbolt 4 Materialien mit geringerem Verlust (Df < 0,010 bei 10 GHz), um die Signalintegrität über Entfernungen auf der Platine aufrechtzuerhalten.

- Glasübergangstemperatur (Tg): Hoch-Tg-Materialien (Tg > 170°C) sind zwingend erforderlich, um der erheblichen thermischen Beanspruchung in engen Gehäusen standzuhalten und mehrere Reflow-Zyklen während der beidseitigen SMT-Montage zu überstehen.

- CTI (Comparative Tracking Index): Ausreichende CTI-Werte verhindern elektrische Durchschläge bei enger Leiterbahnführung in feuchten Umgebungen.

Anforderungen an das Routing von DDR5-Speicherschnittstellen

Der Übergang zu DDR5-Speichern in Laptops führt beispiellose Herausforderungen an die Signalintegrität ein. Mit Datenraten, die 5600 MT/s überschreiten, erfordert die Speicherschnittstelle – sei es auf SO-DIMMs geroutet oder direkt auf das Motherboard gelötet (LPDDR5) – strenge High-Speed-Design-Lösungen.

DDR5 implementiert eine Zwei-Kanal-Architektur pro Modul, ein modifiziertes Takt-Schema (Clocking) und integrierte PMICs (Power Management ICs), die alle die PCB-Routing-Strategien grundlegend verändern.

Richtlinien für das DDR5-Routing

- Topologie: SO-DIMM-Konfigurationen verwenden typischerweise eine Daisy-Chain-Topologie für Befehls-/Adresssignale (Command/Address) mit spezifischen Längenanforderungen zwischen den Modulen. LPDDR5 verwendet aufgrund der kürzeren Entfernungen häufig Punkt-zu-Punkt-Verbindungen.

- Längenanpassung (Length Matching): Strenge Längenanpassung ist entscheidend. Datenspuren innerhalb einer Byte-Gruppe (Byte Lane) müssen im Allgemeinen auf ±1 mm (oft enger, in ps spezifiziert) an ihr zugehöriges DQS (Data Strobe)-Signal angepasst werden.

- Lagenübergänge (Layer Transitions): Minimieren Sie Via-Übergänge für High-Speed-Signale. Wenn Vias notwendig sind, verwenden Sie benachbarte Ground-Return-Vias innerhalb von 1 mm, um einen kontinuierlichen Rückstrompfad aufrechtzuerhalten und Impedanzsprünge zu vermeiden.

- Vermeidung von Übersprechen (Crosstalk Avoidance): Halten Sie ausreichend Abstand (typischerweise 3W-Regel) zwischen den Signalen auf derselben Lage ein und leiten Sie benachbarte Lagen orthogonal zueinander (obwohl Stripline-Routing bevorzugt wird, um Broadside-Kopplung zu vermeiden).

- Referenzlagen (Reference Planes): Daten-, Adress- und Taktsignale müssen über durchgehende, ununterbrochene Masse-Referenzlagen (Ground Reference Planes) geroutet werden. Das Routen über Splits in Stromversorgungs- oder Masselagen verursacht schwerwiegende Signalverschlechterung und EMI-Probleme.

Design des CPU- und GPU-Stromversorgungsnetzwerks

Moderne Laptop-Prozessoren weisen schnelle transiente Stromanforderungen auf; sie können in Mikrosekunden vom Ruhezustand auf maximalen Turbo-Boost-Zustand wechseln und dabei Ströme von über 100 A ziehen. Ein robustes Stromversorgungsnetzwerk (PDN) ist entscheidend, um Spannungseinbrüche und -überschwinger zu verhindern, die eine Systeminstabilität verursachen können.

Dieses PDN umfasst Spannungsreglermodule (VRMs), die Kupferebenen der PCB und ein carefully dimensioniertes Entkopplungskondensator-Netzwerk.

PDN-Design-Prinzipien

- VRM-Platzierung: Positionieren Sie Spannungsregler so nah wie möglich an der CPU/GPU, um Gleichstromwiderstand (IR-Drop) und Induktivität auf der Platine zu minimieren. In High-End-Gaming-Laptops nehmen VRM-Komponenten oft einen erheblichen Teil der Platinenfläche um den Prozessor herum ein.

- Design der Stromversorgungsebenen (Power Plane Design): Verwenden Sie dedizierte, breite Kupferflächen für die Hauptstromschienen (Core, Graphics, Memory). Minimieren Sie Engpässe und Perforationen (Vias) in diesen Ebenen, die den Widerstand und die Induktivität erhöhen. Das Überlappen von Stromversorgungs- und Masselagen mit ultradünnen Dielektrika maximiert die Platinenkapazität für hochfrequente Entkopplung.

- Strategie zur Platzierung von Entkopplungskondensatoren:

- Bulk-Kondensatoren (Tantal oder große MLCCs): In der Nähe der VRM-Ausgänge platzieren, um niederfrequente Transienten zu bewältigen.

- Keramische Kondensatoren (MLCCs, 0402/0201): So nah wie möglich an den Versorgungspins des Prozessors platzieren, idealerweise direkt auf der gegenüberliegenden Seite der Platine (Bottom Side) unter dem BGA.

- Via-Platzierung für Kondensatoren: Verwenden Sie Via-in-Pad oder Vias in unmittelbarer Nähe der Kondensator-Pads, um die parasitäre Induktivität der Befestigung (ESL) zu minimieren.

- Thermische Aspekte der Stromversorgung (Thermal Power Considerations): Hochstrom-Leiterbahnen erzeugen erhebliche Joule-Erwärmung (I²R). Verwenden Sie Polygon-Pours anstelle von Leiterbahnen für die Stromführung, wo immer dies möglich ist.

Wärmemanagement durch PCB-Design

Laptop-Kühlsysteme stützen sich stark auf Heatpipes, Dampfkammern (Vapor Chambers) und Lüfter, aber die PCB selbst spielt eine entscheidende Rolle beim Wärmemanagement. Unzureichendes thermisches PCB-Design führt zu lokalen Hotspots (Hitzestaus), drosselt die Prozessorleistung (Thermal Throttling) und verringert die Lebensdauer der Komponenten.

Die Leiterplatte unterhalb von Prozessor-Packages dient als anfänglicher Wärmeverteiler (Heat Spreader) – thermische Vias leiten die Wärme von der Top-Layer-BGA-Verbindung zu inneren Kupferebenen und der unteren Oberfläche. Für Komponenten ohne direkten Kontakt zum Kühlkörper (Chipsatz, Spannungsregler, Speicher) ist die PCB möglicherweise der primäre Wärmepfad, wodurch die Flächenabdeckung mit Kupfer entscheidend wird.

Ansätze für das thermische PCB-Design

- Thermische Via-Arrays (Thermal Via Arrays): Dichte Via-Arrays (0,3 mm Bohrdurchmesser, 0,5 mm Abstand) unter Prozessor- und GPU-Packages leiten die Wärme vertikal ab; gefüllte Vias verhindern das Einziehen von Lot und verbessern die thermische Kontinuität.

- Nutzung der Kupferebenen: Maximieren Sie die Kupferabdeckung auf den inneren Lagen unterhalb thermisch kritischer Komponenten; verwenden Sie 2 oz Kupfer auf thermischen Lagen, falls der Lagenaufbau dies zulässt.

- Komponenten-Wärmeleitpads (Thermal Pads): VRMs, Chipsätze und andere Komponenten mittlerer Leistung nutzen häufig Wärmeleitpads, die mit den Masseflächen des Gehäuses verbunden sind; die PCB muss an diesen Kontaktpunkten eine ausreichende Kupferfläche bieten.

- Befestigung von Kühlkörpern (Heat Sink Mounting): Laptop-Kühlkörper werden über Federclips oder Schrauben montiert; die Befestigungslöcher der PCB müssen (falls nicht geerdet) elektrische Isolierung und mechanischen Halt ohne Rissbildung bieten.

- Management der thermischen Ausdehnung: Große Prozessor-Packages (45 mm+) weisen unterschiedliche Ausdehnungskoeffizienten im Vergleich zur PCB auf; ausreichendes Underfill und ein geeignetes Design der Lötstellen verhindern die Ausbreitung von Rissen.

- Temperaturüberwachung: Die Platzierung von thermischen Sensoren (Thermistoren oder Thermodioden in Prozessor-Packages) liefert Feedback für die Lüftersteuerung; stellen Sie sicher, dass Sensoren eine gute thermische Kopplung zu den überwachten Komponenten aufweisen.

Die Integration des thermischen PCB-Designs mit den Kühlsystemen des Systems erfordert ein Verständnis sowohl der Prinzipien des thermischen Managements als auch der mechanischen Schnittstellenanforderungen.

Fertigungsüberlegungen für Laptop-Motherboards

Die Fertigung von Laptop-Motherboards kombiniert moderate HDI-Komplexität (Blind-/Buried-Vias für BGA-Fanout) mit Anforderungen an eine hochvolumige Produktion und Qualitätserwartungen, die sich Automobilstandards annähern. Große OEMs – Dell, HP, Lenovo, Apple – erlegen Lieferanten-Qualifizierungsanforderungen auf, einschließlich Prozessfähigkeitsuntersuchungen, statistischer Prozesskontrolle und laufender Zuverlässigkeitsüberwachung.

Die für CPUs und PCHs verwendeten Fine-Pitch-BGA-Packages (0,4-0,8 mm Pitch) erfordern präzise Bohrregistrierung, kontrollierte Kupferabscheidung und einen konsistenten Lötstopplack-Auftrag. Fertigungsabweichungen wirken sich direkt auf die Ausbeute bei der Bestückung aus – eine schlecht kontrollierte Via-Registrierung oder Ausrichtung des Lötstopplacks verursacht Bestückungsfehler, die erst nach dem teuren Aufsetzen der Komponenten zutage treten.

Fertigungsanforderungen

- HDI-Fähigkeit: Viele Laptop-Designs erfordern Blind-Vias (1+N+1 oder 2+N+2 Strukturen) für ein angemessenes BGA-Fanout; Via-in-Pad mit gefüllter und gekappter (capped) Konstruktion für maximale Routing-Dichte.

- Bohrregistrierung (Drill Registration): Registrierung von Blind-Vias auf darunterliegende Lagen innerhalb von ±50 μm; Lagen-zu-Lagen-Ausrichtung über alle Schichten innerhalb von ±75 μm.

- Qualität des Lötstopplacks: LPI-Lötstopplack (Liquid Photo-Imageable) mit kontrollierter Stegbreite (Dam Width) zwischen Fine-Pitch-Pads; Registrierung auf Merkmale innerhalb von ±50 μm.

- Oberflächenfinish: ENIG wird für die Zuverlässigkeit von Fine-Pitch-BGAs bevorzugt; eine kontrollierte Dicke (3-5 μin Au, 100-200 μin Ni) verhindert sowohl exzessives als auch unzureichendes Gold.

- Impedanzkontrolle: DDR5- und PCIe-Leiterbahnen erfordern eine Impedanztoleranz von ±8 %; nachgewiesen durch TDR-Messung an Produktions-Testcoupons.

- Nutzen-Auslastung (Panel Utilization): Platinengröße und Panel-Optimierung beeinflussen die Kosten; unregelmäßige Laptop-Formen können die Panel-Auslastung auf unter 70 % begrenzen – eine Designüberlegung während der frühen Entwicklung.

Die Auswahl von Fertigungspartnern mit nachgewiesenen Fähigkeiten in der PCB-Fertigung für HDI-Strukturen und Fine-Pitch-Anwendungen stellt sicher, dass Designs sich in eine produzierbare Serienfertigung umsetzen lassen.

Zuverlässigkeitsprüfung und Qualitätsanforderungen

Laptops sind hohen Erwartungen an die Zuverlässigkeit ausgesetzt – Verbraucher erwarten mehr als 5 Jahre Nutzungsdauer mit täglichen Nutzungsmustern, die Temperaturwechsel (Sleep-Wake-Zyklen verursachen wiederholte Temperaturübergänge), mechanische Belastungen (Öffnen/Schließen, Tragen in Taschen) und Umwelteinflüsse (Feuchtigkeit, Staub) beinhalten. Die Qualität und Zuverlässigkeit der Leiterplatte wirkt sich direkt auf Garantiekosten und den Ruf der Marke aus.

Große OEMs spezifizieren umfangreiche Qualifikationstests, die über die Standard-IPC-Abnahmekriterien hinausgehen. Typische Anforderungen umfassen beschleunigte Temperaturwechsel (1000+ Zyklen, -40°C bis +105°C), Feuchtigkeitseinwirkung (85°C/85 % RH für 1000 Stunden), mechanische Schocks und Vibrationen sowie thermische Zyklen unter Spannung (Powered Thermal Cycling), die reale Nutzungsbedingungen simulieren.

Rahmenbedingungen für Qualität und Zuverlässigkeit

- IPC-Klasse 2/3: Die meisten Laptop-PCBs erfordern mindestens IPC-6012 Klasse 2; Premium-Produkte und Business-Class-Laptops können Klasse 3 für engere Toleranzen und verbesserte Zuverlässigkeit erfordern.

- Schliffbild-Inspektion (Microsection Inspection): Querschnittsanalysen verifizieren die Qualität der Kupferbeschichtung, die Integrität der Via-Struktur und die Dielektrikumsdicke; durchgeführt an Qualifizierungslosen und als fortlaufende Produktionsstichprobe.

- Elektrischer Test: 100 % Durchgangs- und Isolationstest mittels Flying Probe oder Fixture; Verifizierung der kontrollierten Impedanz auf High-Speed-Leiterbahnen.

- Temperaturwechsel (Thermal Cycling): Die Qualifizierung umfasst umfangreiche Temperaturwechsel; Ausfallkriterien sind der Anstieg des Via-Widerstands, Delamination von Laminaten und Rissbildung im Lötstopplack.

- CAF-Beständigkeit: Tests auf leitfähige anodische Filamente (CAF) verifizieren die Beständigkeit gegenüber elektrochemischer Migration zwischen eng beieinanderliegenden Leitern; kritisch für Fine-Pitch-Designs.

- Rückverfolgbarkeit (Traceability): Lückenlose Chargen-Rückverfolgbarkeit von den Laminatmaterialien bis hin zu fertigen Platinen; essenziell für die Korrelation von Fehleranalysen und kontinuierliche Verbesserung.

Robuste Qualitätsmanagementsysteme mit dokumentierten Verfahren, kalibrierten Geräten und geschultem Personal bilden die Grundlage für eine gleichbleibende Laptop-PCB-Qualität.

Technische Zusammenfassung

Das PCB-Design für Laptop-Motherboards balanciert konkurrierende Anforderungen aus: High-Speed-Signalintegrität für DDR5- und PCIe-Schnittstellen, robuste Stromversorgung für hoch-TDP Prozessoren, Wärmemanagement in engen Formfaktoren und Fertigungsqualität, die langfristige Zuverlässigkeit sichert. Der Erfolg erfordert ein integriertes Design, das alle Aspekte gleichzeitig berücksichtigt, anstatt jeden einzeln zu optimieren.

Zu den wichtigsten frühen Entscheidungen in der Laptop-Entwicklung gehören die Lagenanzahl und Lagenaufbau-Architektur (bestimmen Signalintegrität und Stromversorgungsfähigkeit), das HDI-Komplexitätsniveau (beeinflusst Kosten und Fertigungskomplexität), die thermische Strategie (Rolle der Leiterplatte im gesamten Kühlsystem) und Ziele für Qualität/Zuverlässigkeit (bestimmen die Materialauswahl und Fertigungsanforderungen).

Die Beziehung zum PCB-Fertigungspartner erweist sich als kritisch – Laptop-Programme umfassen eine signifikante Volumenproduktion mit aggressiven Kostenzielen, dennoch nähern sich die Qualitätsanforderungen denen der Automobilindustrie an. Fertigungsfähigkeit, Prozessreife und Qualitätssysteme fließen alle zusammen mit Kostenüberlegungen in die Partnerwahl ein.