Eine speicherprogrammierbare Steuerung (SPS) führt Echtzeit-Steuerlogik aus und kommuniziert über digitale und analoge E/A-Kanäle mit Dutzenden – manchmal Hunderten – von Feldgeräten. Die Leiterplatte muss die Signalintegrität in elektrisch feindlichen Fabrikumgebungen aufrechterhalten, in denen Motorantriebe, Schweißgeräte und Schaltschütze kontinuierlich leitungsgebundene und abgestrahlte Störungen erzeugen.

Dieser Leitfaden behandelt das Engineering auf PCB-Ebene, das bestimmt, ob eine SPS über eine 20-jährige Lebensdauer unter industriellen Bedingungen zuverlässig funktioniert – oder unvorhersehbar ausfällt, wenn die Produktionsanforderungen ihren Höhepunkt erreichen.

In diesem Leitfaden

- E/A-Isolationsarchitektur

- Industrielle EMV und Störfestigkeit

- Modulares Backplane-Design

- Stromverteilung und Schutz

- Wärmemanagement in Gehäusen

- Fertigung für industrielle Zuverlässigkeit

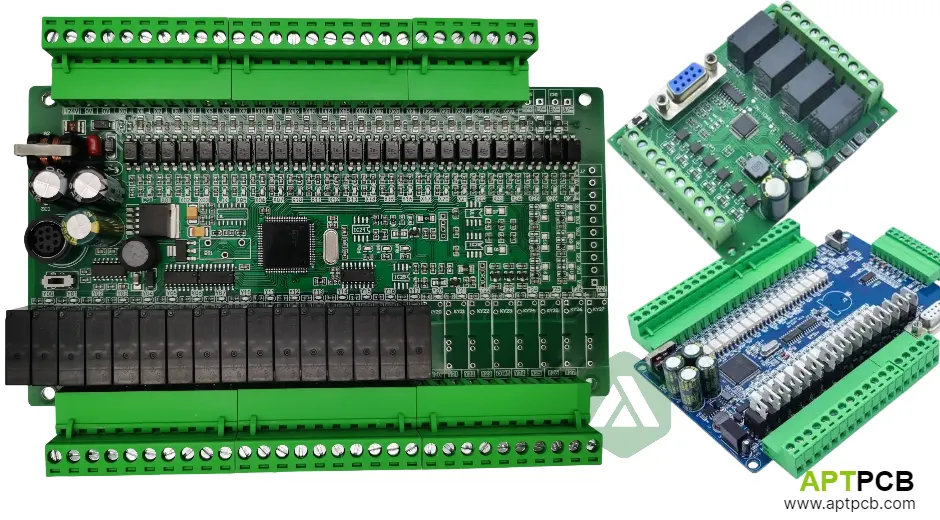

E/A-Isolationsarchitektur

SPS-E/A-Schnittstellen verbinden sich direkt mit der Feldverkabelung, die Transienten über 2 kV während des Schaltschützschaltens oder bei Erdschlussereignissen führen kann. Galvanische Trennung verhindert, dass sich diese Störungen auf den Prozessor ausbreiten und die Steuerlogik beschädigen – eine sicherheitskritische Anforderung in der industriellen Automatisierung.

Die Isolierung auf Optokopplerbasis ist nach wie vor für digitale E/A üblich, wobei Hochgeschwindigkeitsoptokoppler (10+ Mbit/s) schnellere Scanzeiten ermöglichen. Das PCB-Layout muss Kriech- und Luftstrecken gemäß IEC 60664-1 einhalten, basierend auf dem Verschmutzungsgrad (typischerweise PD3 für Industrieumgebungen) und der Arbeitsspannung. Für 24-VDC-E/A, die in PD3-Umgebungen betrieben werden, erreicht die minimale Kriechstrecke 4 mm auf PCB-Oberflächen.

Digitale Isolator-ICs mit kapazitiver oder magnetischer Kopplung bieten eine höhere Geschwindigkeit und geringere Leistung als Optokoppler. Diese Geräte erfordern eine sorgfältige Beachtung der Gleichtakttransientenimmunität (CMTI) – der Fähigkeit, schnelle Gleichtaktspannungsänderungen ohne Fehlauslösung zurückzuweisen. Digitale Isolatoren in Industriequalität spezifizieren eine CMTI von über 50 kV/μs.

Implementierung der E/A-Isolation

- Kriechstrecke: Halten Sie je nach Arbeitsspannung und Verschmutzungsgrad gemäß IEC 60664-1 4–8 mm zwischen isolierten Bereichen ein.

- Isolationsbarrieren-Routing: Keine Leiterbahnen, Kupferflächen oder Vias kreuzen die Isolationsbarriere, außer durch qualifizierte Isolationskomponenten.

- Verstärkte Isolierung: Sicherheitsbewertete E/A verwenden verstärkte Isolierung (5 kVrms Isolationsbewertung) mit verdoppelten Kriechstreckenanforderungen.

- Masseflächenteilungen: Isolierte Masseflächen verbinden sich nur über den internen Kopplungsmechanismus des Isolationsgeräts.

- Transientenschutz: TVS-Dioden und Varistoren an feldseitigen E/A klemmen Transienten ab, bevor sie Isolationsbarrieren belasten.

- Kanal-zu-Kanal-Isolierung: Module mit hoher Kanalzahl erfordern möglicherweise eine Isolierung zwischen Kanalgruppen, nicht nur eine Feld-zu-Logik-Isolierung.

Industrielle EMV und Störfestigkeit

Fabrikböden stellen EMV-Herausforderungen dar, die typische kommerzielle Umgebungen in den Schatten stellen. Frequenzumrichter erzeugen leitungsgebundene Emissionen von Gleichstrom bis zu zehn MHz; Lichtbogenschweißgeräte erzeugen breitbandiges Impulsrauschen; Relaisspulen erzeugen induktive Rückschlagtransienten. Die SPS-PCB muss diese Störungen zurückweisen und gleichzeitig Emissionsgrenzwerte einhalten, die Störungen empfindlicher Geräte in der Nähe verhindern.

Die Prüfung der Störfestigkeit gegen leitungsgebundene Störgrößen gemäß IEC 61000-4-6 erfordert die Zurückweisung von 10 Vrms HF-Strömen, die von 150 kHz bis 80 MHz auf E/A- und Stromleitungen injiziert werden. Die Störfestigkeit gegen schnelle Transienten (Burst) gemäß IEC 61000-4-4 wendet 2-kV-Schnelltransienten-Bursts mit einer Wiederholungsrate von 5 kHz an. Die Störfestigkeit gegen Stoßspannungen (Surge) gemäß IEC 61000-4-5 setzt das Gerät 2-kV-Stoßspannungen Phase-Erde und 1-kV-Stoßspannungen Phase-Phase aus. Diese Tests spiegeln reale Industriestörungen wider.

Die Netzteilfilterung auf industriellen Leistungs-PCB-Designs kombiniert Gleichtaktdrosseln, X- und Y-Kondensatoren und Ferritperlen, um leitungsgebundene Emissionen zu dämpfen und Immunität zu bieten. Die Filtereckfrequenz muss niedrig genug sein, um Industrierauschen zurückzuweisen, während das Einschwingverhalten des Netzteils erhalten bleibt.

EMV-Designstrategien

- Mehrstufige Filterung: Kaskadierte Filterstufen adressieren unterschiedliche Frequenzbereiche – LC-Filter für niedrige Frequenzen, Ferrite für hohe Frequenzen.

- Schirmpartitionierung: Metallabschirmungen oder PCB-Abschirmdosen isolieren empfindliche analoge Abschnitte von rauschbehafteten Digital- und Leistungsschaltungen.

- Integrität der Massefläche: Ununterbrochene Masseflächen unter Signalleiterbahnen bieten Rückwege mit niedriger Impedanz, die den Schleifenbereich minimieren.

- Steckerfilterung: Gefilterte Steckverbinder oder auf der Leiterplatte montierte Filter an E/A-Eintrittspunkten stoppen Rauschen an der Grenze.

- Kabelabschirmungsterminierung: Eine 360-Grad-Abschirmungsterminierung zur Gehäusemasse verhindert, dass Schirmströme in PCB-Massen einkoppeln.

- Spread Spectrum Clocking: Prozessor- und Kommunikationstakte verwenden Spread Spectrum, um Spitzenemissionen bei harmonischen Frequenzen zu reduzieren.

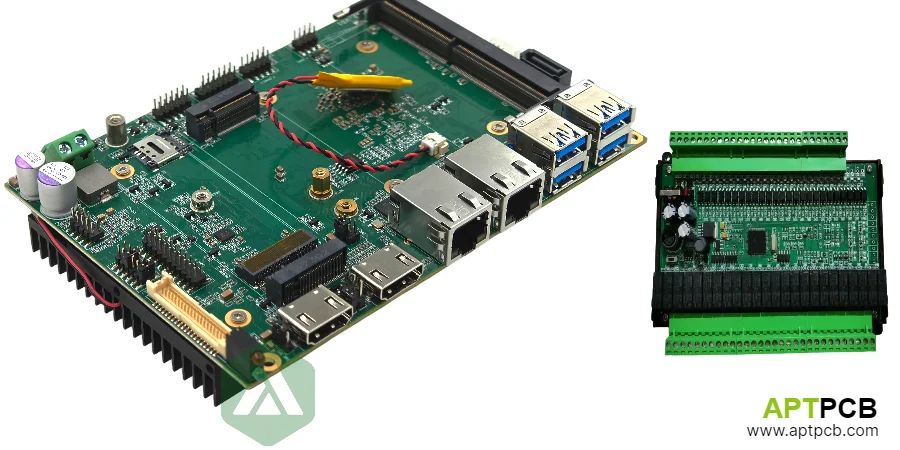

Modulares Backplane-Design

Moderne SPSen verwenden modulare Architekturen, bei denen eine Backplane-Platine Prozessor, Stromversorgung und E/A-Module miteinander verbindet. Diese Backplane trägt digitale Hochgeschwindigkeitsbusse, analoge Signale und erhebliche Gleichstromleistung – und ermöglicht gleichzeitig Hot-Swap-Fähigkeit in einigen Systemen. Der Mehrlagen-PCB-Stackup muss diese vielfältigen Anforderungen ohne Übersprechen oder Power-Integrity-Probleme erfüllen.

Backplane-Busse in aktuellen SPSen reichen von proprietären parallelen Schnittstellen bis hin zu Standardprotokollen wie EtherCAT, PROFINET oder proprietären seriellen Hochgeschwindigkeitsverbindungen mit mehr als 100 Mbit/s. Hochgeschwindigkeitsserielles reduziert die Pinzahl, erfordert jedoch Leiterbahnen mit kontrollierter Impedanz und sorgfältige Beachtung der Einfügungsdämpfung über Backplane-Steckverbinder.

Die Steckverbinderauswahl gleicht Zuverlässigkeit, Dichte und Hot-Swap-Anforderungen aus. Hochzuverlässige Steckverbinder mit gasdichten Schnittstellen widerstehen Korrosion in Industrieatmosphären. Versetzte Strom- und Massepins ermöglichen das Einsetzen von Modulen ohne Störungen bei laufenden Modulen – entscheidend für Live-Wartungsszenarien.

Backplane-Engineering-Anforderungen

- Impedanzkontrolle: Serielle Hochgeschwindigkeitsspuren erfordern eine Impedanztoleranz von ±10 %; differenzielle Paare benötigen eine Längenanpassung innerhalb von 5 mils.

- Stromverteilung: Schwere Kupferflächen (2–4 oz) verteilen 24-VDC-Backplane-Leistung an Module mit minimalem Spannungsabfall.

- Steckverbinderzuverlässigkeit: Steckverbinder in Industriequalität, ausgelegt für 500+ Steckzyklen mit gasdichten Kontakten für Korrosionsbeständigkeit.

- Übersprechmanagement: Schutzleiterbahnen oder Massereferenzen zwischen Hochgeschwindigkeits- und empfindlichen analogen Kanälen.

- Hot-Swap-Sequenzierung: Versetzte Pinlängen stellen sicher, dass Masse vor Strom beim Einsetzen des Moduls verbunden wird.

- Mechanische Unterstützung: Die Backplane-Montage bietet ausreichende mechanische Unterstützung für den Modulerhalt unter Vibration.

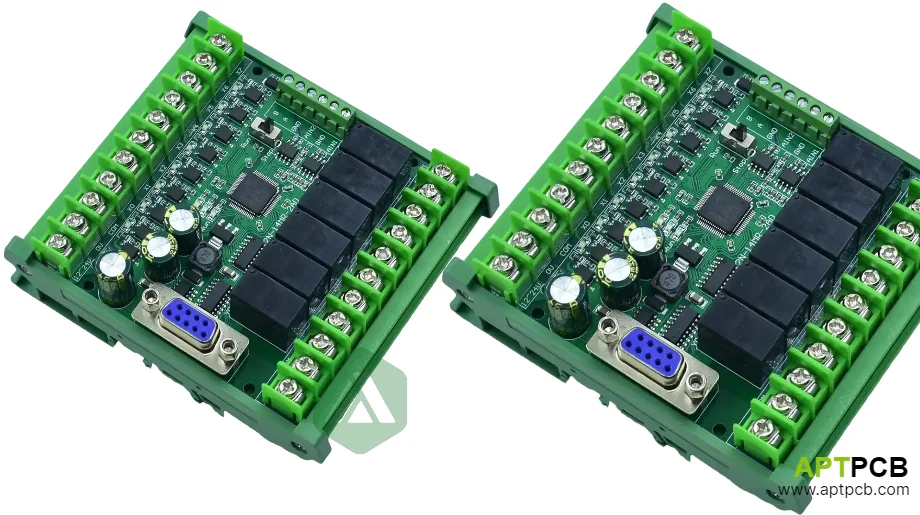

Stromverteilung und Schutz

SPSen arbeiten typischerweise mit 24 VDC nominal mit Toleranzbereichen von 20–28 VDC, obwohl einige Systeme Wechselstromnetze direkt akzeptieren. Das PCB-Stromverteilungsnetzwerk muss die Regelung unter Lasttransienten aufrechterhalten und gleichzeitig vor Verpolung, Überspannung und transienten Ereignissen schützen, die industrielle Umgebungen regelmäßig erzeugen.

Eingangsschutzschaltungen auf Industriesteuerungs-PCBs umfassen Verpolungsschutz (ideale Diode oder P-Kanal-MOSFET), Überspannungsschutz (TVS- oder Crowbar-Schaltungen) und Einschaltstrombegrenzung. Diese Schutzmaßnahmen dürfen den normalen Betrieb nicht beeinträchtigen – der Durchlassspannungsabfall beeinflusst die Effizienz, und die Schutzreaktionszeit muss schneller sein als die Schadensschwellen der Schaltung.

Multi-Rail-Leistungsarchitekturen bedienen verschiedene Schaltungsbereiche: 3,3 V oder 5 V für digitale Logik, ±15 V oder 24 V für analoge E/A, isolierte Versorgungen für Kommunikationsschnittstellen. Jede Schiene erfordert eine geeignete Regelung, Filterung und Sequenzierung, um einen zuverlässigen Start und Betrieb zu gewährleisten.

Stromsystemdesign

- Eingangsschutz: Verpolung (100 V+ Sperrung), TVS-Überspannungsschutz, rückstellbare Sicherung für Überstrom.

- Einschaltbegrenzung: NTC-Thermistor oder aktive Begrenzung verhindert das Auslösen vorgeschalteter Leistungsschalter beim Einschalten.

- Regelungseffizienz: Schaltregler mit 90 %+ Effizienz minimieren die Wärmeentwicklung in geschlossenen Installationen.

- Sequenzierung: Stromschienen starten in definierter Reihenfolge, um Latch-up oder unsachgemäße Initialisierung zu verhindern.

- Bulk-Kapazität: Überbrückungskondensatoren erhalten den Betrieb während kurzer Stromunterbrechungen aufrecht (10–20 ms typisch).

- Überwachung: Spannungsüberwacher erkennen Außer-Bereich-Zustände und lösen ein geordnetes Herunterfahren oder eine Fehleranzeige aus.

Wärmemanagement in Gehäusen

SPSen werden in elektrischen Gehäusen montiert, in denen die Umgebungstemperatur 55–60 °C erreichen kann und die natürliche Konvektion begrenzt ist. Das PCB- und Gehäusedesign muss intern erzeugte Wärme abführen, ohne auf Zwangsluftkühlung angewiesen zu sein – viele Industrieumgebungen verbieten Lüfter aufgrund von Staubkontaminationsbedenken.

Komponentenplatzierung und Kupferverteilung auf Wärmemanagement-PCBs verteilen Wärme über die verfügbare Oberfläche. Leistungshalbleiter verbinden sich mit internen Kupferflächen, die Wärme an Gehäuseoberflächen oder Kühlkörper leiten. Thermische Vias unter Komponenten reduzieren den thermischen Widerstand von Übergang zu Umgebung um 30–50 % im Vergleich zur reinen Oberflächenkühlung.

Industrielle Temperaturgrade reichen von -40 °C bis +85 °C Umgebungstemperatur, was sich in Sperrschichttemperaturen von über 100 °C unter Worst-Case-Bedingungen niederschlägt. Die Komponentenauswahl muss das Derating bei extremen Temperaturen berücksichtigen – insbesondere Elektrolytkondensatoren leiden unter einer drastisch verkürzten Lebensdauer bei erhöhten Temperaturen.

Ansätze für thermisches Design

- Kupferverteilung: 2–4 oz Kupferflächen leiten Wärme von konzentrierten Quellen zu größeren Strahlungsbereichen.

- Thermische Via-Arrays: Via-Arrays unter Leistungsgeräten reduzieren den thermischen Widerstand zu inneren oder unteren Kupferflächen.

- Komponentenplatzierung: Heiße Komponenten in der Nähe von Gehäuseoberflächen oder Lüftungspfaden positioniert, nicht in thermischen Totzonen.

- Kondensatorauswahl: Polymer- oder Keramikkondensatoren ersetzen Elektrolyte in heißen Zonen, um die Zuverlässigkeit zu verbessern.

- Schutzlackierung: Berücksichtigen Sie thermische Auswirkungen – einige Beschichtungen behindern die Konvektion und verbessern gleichzeitig die Feuchtigkeitsbeständigkeit.

- Gehäuseintegration: Das Design koordiniert mit dem Gehäusehersteller, um Wärmepfade zu Außenflächen zu optimieren.

Fertigung für industrielle Zuverlässigkeit

Industrielle SPSen erfordern Fertigungsprozesse, die eine Lebensdauer von 20+ Jahren mit minimalen Feldausfällen gewährleisten. Dies erfordert strengere Prozesskontrollen, 100 % Tests und Materialauswahl, die über typische kommerzielle Standards hinausgeht. Die PCB-Herstellung und Montageprozesse müssen diese Qualitätsstufen über Produktionsvolumina hinweg aufrechterhalten.

Die Auswahl des PCB-Substrats begünstigt Materialien mit hohem Tg (Tg ≥ 170 °C), die sowohl Montagetemperaturen als auch Langzeitbetrieb bei erhöhten Temperaturen standhalten. Kupferhaftung und Beschichtungsqualität beeinflussen die Langzeitzuverlässigkeit unter Temperaturwechselbeanspruchung – schlechte Haftung führt nach Tausenden von Temperaturzyklen zum Abheben der Leiterbahnen.

Die Zuverlässigkeit der Lötverbindung hängt von der ordnungsgemäßen intermetallischen Bildung, dem Fehlen von Hohlräumen und der geeigneten Kehlgeometrie ab. Röntgeninspektion verifiziert BGA- und QFN-Lötverbindungen, die visuelle Inspektion nicht bewerten kann. Funktionstests validieren E/A-Isolierung, analoge Genauigkeit und Kommunikationsschnittstellen vor dem Versand.

Qualitätsanforderungen an die Fertigung

- IPC-Klasse 3: Industrieelektronik erfordert Verarbeitung der Klasse 3 gemäß IPC-A-610 für höchste Zuverlässigkeit.

- Lötstelleninspektion: 100 % AOI mit statistischer Röntgenstichprobe für verdeckte Verbindungen.

- Burn-In-Test: Optionaler Lebensdauertest fängt Ausfälle aufgrund von Frühsterblichkeit vor dem Versand ab.

- Schutzlackierung: Selektive Beschichtung schützt vor Feuchtigkeit und Kontamination, während Wärmepfade frei bleiben.

- Rückverfolgbarkeit: Vollständige Komponenten- und Prozessrückverfolgbarkeit ermöglicht Ursachenanalyse bei Auftreten von Feldausfällen.

- Umweltprüfung: Stichprobenprüfung gemäß IEC 60068 validiert Temperatur-, Feuchtigkeits- und Vibrationsleistung.

Zusammenfassung

SPS-PCB-Design gleicht die widersprüchlichen Anforderungen von Störfestigkeit, Wärmemanagement, modularer Flexibilität und Langzeitzuverlässigkeit aus. Erfolg erfordert das Verständnis der Realitäten der Industrieumgebung – transiente Ereignisse, die in Kilovolt gemessen werden, Umgebungstemperaturen, die Komponentennennwerte herausfordern, und Lebenserwartungen über Jahrzehnte. Die während des Designs getroffenen PCB-Engineering-Entscheidungen bestimmen, ob die SPS während ihres gesamten geplanten Lebenszyklus zuverlässig funktioniert oder zu einer Wartungsbelastung wird, die die Produktion stört.