Die nackte Leiterplatte ist fertig. Sie hat TDR-Impedanztests, Schliffbildprüfung und die Verifikation der Rogers-Materialcharge bestanden. Jetzt geht sie in die SMT-Bestückung und damit beginnt eine zweite Gruppe möglicher Ausfallmechanismen, die der Fertigungsprozess allein nicht verhindern kann.

Die Bestückung von RO3003-Leiterplatten ist in vier konkreten Bereichen anspruchsvoller als eine Standard-FR-4-Bestückung: Feuchtemanagement vor dem Einschleusen in die Linie, Schablonendesign der Lötpaste für Thermal-Pad-Via-Strukturen, Reflow-Atmosphäre und Temperaturprofil sowie die Prüfung verborgener Lötstellen nach der Bestückung. Für jeden dieser Punkte gibt es eine klar definierte Best Practice. Wird auch nur einer davon ausgelassen, zeigt sich das als Voiding unter dem Thermal Pad, als Delamination an der PTFE/FR-4-Hybridgrenzfläche oder als Lötstellenfehler, die bereits in den ersten hundert Temperaturzyklen auftreten.

Dieser Leitfaden behandelt alle vier Punkte im Detail: welches Problem jeweils vorliegt, wie die Prozesslösung aussieht und welche Akzeptanzkriterien gelten.

Vier Bestückungsvariablen, die FR-4-Standardprozesse nicht beherrschen

Bevor wir die einzelnen Bestückungsschritte durchgehen, ist es sinnvoll, genau zu verstehen, was RO3003 von Standard-FR-4 unterscheidet und warum übliche FR-4-Parameter hier nicht nur unpassend, sondern aktiv fehlerverursachend sein können.

Immersion-Silver-Oberfläche. Die meisten für HF optimierten RO3003-Leiterplatten kommen mit ImAg-Oberfläche an. Das ist die bevorzugte Wahl, weil die dünne, plane Schicht bei hohen Frequenzen elektromagnetisch transparent ist. Anders als ENIG läuft ImAg bei Kontakt mit Schwefelverbindungen oder erhöhten Temperaturen an. Es verlangt eine Stickstoff-Reflow-Atmosphäre und ein präzises thermisches Profil, wie es Standard-FR-4-Linien mit Luft-Reflow nicht liefern.

Feuchteempfindlichkeit des Hybridsubstrats. Obwohl RO3003 selbst fast keine Feuchtigkeit aufnimmt (0,04 %), sind die inneren FR-4-Lagen einer Hybridleiterplatte hygroskopisch. Feuchtigkeit, die während eines Reflow-Zyklus bei 250°C bis an die Bonding-Grenzfläche zwischen RO3003 und FR-4 wandert, kann schlagartig zu Dampf werden und interne Delamination verursachen. Vorbake-Protokolle müssen sich also auf die FR-4-Lagen beziehen und dürfen die Leiterplatte nicht einfach als Einmaterial-System behandeln.

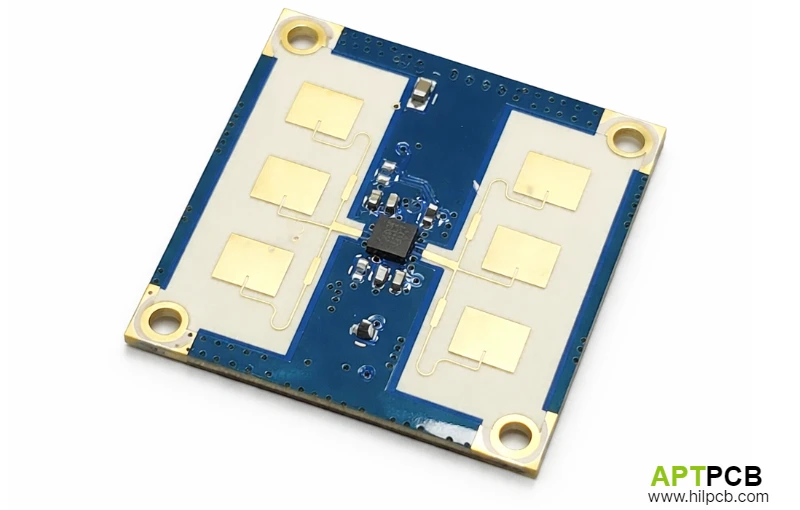

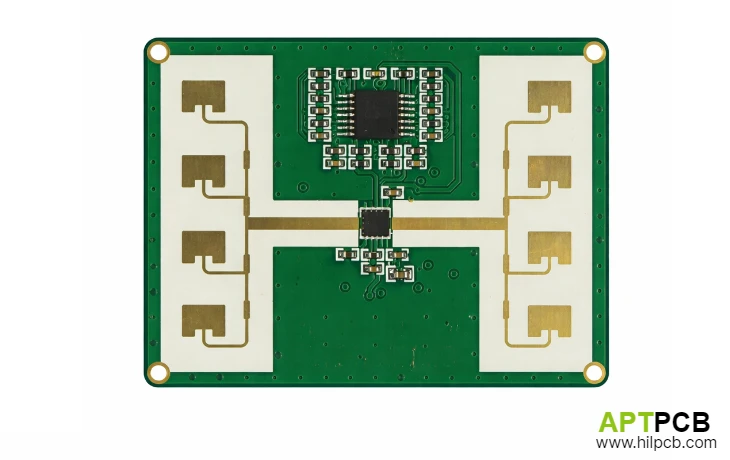

POFV-Thermal-Via-Arrays. Überplattete, verfüllte Vias unter den Thermal Pads von HF-Transceivern schaffen eine besondere SMT-Herausforderung: Wird Lötpaste über ein Via-Array gedruckt, kann sie während des Reflows in die Via-Zylinder einsacken, wenn die Schablonenöffnungen nicht darauf abgestimmt sind. Die Folge sind Voids, welche den thermischen Pfad blockieren und sich durch kein Nacharbeiten mehr beheben lassen. Bereits in der Designphase bestimmt die Art des Verfüllens und Kappens der Vias, wie plan die Landefläche ist und damit direkt, wie gleichmäßig die Paste über dem Array abgesetzt wird. Leiterplatten, bei denen die Kappplattierung des POFV nicht bündig mit der Pad-Oberfläche abschließt, zeigen unabhängig von der Schablonengeometrie vorhersehbares Voiding in den abgesenkten Zonen.

Niedrigere maximale Reflow-Spitzentemperatur. Das Ausdehnungsverhalten von PTFE oberhalb von 250°C beginnt die Grenzfläche zwischen der PTFE-Matrix und der Kupferplattierung der Via-Zylinder auf eine Weise zu belasten, die bei FR-4-Leiterplatten nicht auftritt. Dadurch wird das Reflow-Profil auf eine Art eingeschränkt, die im Folgenden genauer beschrieben wird.

Wer diese Randbedingungen schon in der Bestückungsplanung versteht und nicht erst nach dem ersten 3D-Röntgenlauf, trennt eine RO3003-Bestückung mit hoher Ausbeute von teuren Nacharbeitszyklen.

Feuchte-Vorbake: Schutz der Hybridgrenzfläche vor dem Reflow

Die Physik der Dampfdamination

Die übliche Feuchtigkeitsaufnahme von FR-4 liegt nach Lagerung unter normalen Umgebungsbedingungen bei etwa 0,1–0,5 Gewichtsprozent. Bei einer Hybridleiterplatte, die in einem unkontrollierten Lager lag, in einem Container transportiert wurde oder mehrere Tage in der Wareneingangsprüfung stand, können die inneren FR-4-Lagen über jede freiliegende Leiterplattenkante Feuchtigkeit aus der Luft aufnehmen.

Wenn die Leiterplatte im Reflow in den Bereich von 200–250°C ansteigt, wandelt sich das aufgenommene Wasser an der Bonding-Grenzfläche FR-4/RO3003 in Dampf um. Die Volumenausdehnung ist massiv. Kann dieser Dampf nicht entweichen, bevor das Lot erstarrt und die Leiterplatte abkühlt, erzeugt der entstehende Druck Delaminationsblasen an der Hybrid-Bondlinie, die im Querschliff als Trennung zwischen der äußeren RO3003-Lage und dem FR-4-Kern sichtbar sind.

Das ist ein Zuverlässigkeitsfehler mit KO-Charakter. Die delaminierte Leiterplatte besteht jede Lötstelleninspektion und fällt thermisch aus, weil die FR-4/RO3003-Grenzfläche mechanisch nicht mehr kontinuierlich ist.

Vorbake-Protokoll

APTPCB führt bei allen hybriden RO3003/FR-4-Leiterplatten unmittelbar vor dem Einschleusen in die SMT-Linie einen Vorbake durch. Dieser Bake-Zyklus treibt die aufgenommene Feuchtigkeit aus den FR-4-Lagen aus, ohne die ImAg-Oberfläche aggressiv zu oxidieren. Das ist ein Temperatur/Zeit-Kompromiss, der für jeden Leiterplattenaufbau charakterisiert werden muss.

Nach Abschluss des Bake-Vorgangs gehen die Leiterplatten innerhalb weniger Minuten in die SMT-Linie. Eine erneute Exposition an Umgebungsluft zwischen Bake und Reflow bringt wieder Feuchtigkeit ein; der Nutzen des Vorbake ist aufgebraucht, wenn Leiterplatten nach dem Bake stundenlang bei Raumtemperatur warten.

Für Programme, bei denen sich das Zeitfenster zwischen Vorbake und Reflow nicht kontrollieren lässt, etwa wenn die Leiterplatten an einem Standort gebacken und an einem anderen bestückt werden, ist es am sichersten, die Leiterplatten bis zum Einschleusen in Moisture Barrier Bags verschlossen zu halten und den Bake unmittelbar vor der Bestückung einzuplanen. Der Abschluss des Bake sollte mit der Maschinenrüstung abgestimmt werden, nicht mit dem allgemeinen Fertigungsauftrag.

Window-Pane-Schablonendesign: Voiding unter Thermal Pads eliminieren

Warum Vollflächen-Schablonen auf Thermal Pads versagen

Eine Standard-Schablonenöffnung für ein QFN-Thermal-Pad druckt eine einzige zusammenhängende Lotpastefläche über das gesamte Pad. Während des Reflows wird die Flussmittelchemie in der Paste aktiviert, reinigt die Kupferoberfläche und muss durch das schmelzende Lot ausgasen. Auf einem großen, planen Pad mit einem einzigen durchgehenden Pastendepot hat dieser Flussmitteldampf keinen Fluchtweg. Er bildet Voids unter dem Lotbad und bleibt beim Erstarren eingeschlossen.

Bei RO3003-Leiterplatten mit POFV-Arrays unter dem Thermal Pad verschärft sich die Situation: Voids direkt über Via-Säulen blockieren den primären Wärmepfad. Schon ein einzelner großer Void über einem Cluster von Kupfer-Via-Zylindern kann die lokale Sperrschichttemperatur deutlich über den im Thermalkonzept angenommenen Wert anheben. Der dadurch verlorene Margin wirkt sich direkt auf die Zuverlässigkeit des RFIC unter Temperaturwechsel aus.

Window-Pane-Öffnungsdesign

Die Window-Pane-Schablone teilt die Öffnung des Thermal Pads in ein Raster kleinerer Segmente, getrennt durch pastenfreie Stege, typischerweise 0,15–0,20mm breit. Das Prinzip: Während des Reflows entweicht Flussmitteldampf durch die Öffnungen zwischen den Stegen, bevor das Lot erstarrt. Mehrere kleine Pastendepots fließen beim Schmelzen zusammen, die Entgasungskanäle bleiben jedoch lange genug offen, damit das Gas entweichen kann.

Window-Pane-Parameter für RO3003-Thermal-Pad-Strukturen:

- Fläche jedes einzelnen Öffnungssegments: ≤1,5 × 1,5mm

- Stegbreite: 0,15–0,20mm

- Gesamte Pastenabdeckung: 50–80 % der Thermal-Pad-Fläche

- Schablonendicke: 0,12–0,15mm, konsistent zu benachbarten Anschluss-Pads

Diese Öffnungsgeometrie erzeugt in Kombination mit Stickstoff-Reflow, der im nächsten Abschnitt folgt, bei korrekt ausgelegten POFV-Arrays zuverlässig ein Voiding unter 10 % auf dem Thermal Pad. Für die Zahlen im Detail: IPC-A-610 Class 3 legt die Akzeptanzgrenze bei 30 % aggregiertem Voiding fest; die interne APTPCB-Grenze ist mit 20 % strenger. Die unter 10 % sind die tatsächliche Prozessfähigkeit, die in der Produktion mit dieser Schablonengeometrie erreicht wird, also das reale Ergebnis des Prozesses und nicht die Bewertungsgrenze.

Stickstoff-Reflow: Atmosphäre, Profil und Temperaturziele

Warum Stickstoff für ImAg/RO3003-Bestückung erforderlich ist

Luft-Reflow bei Temperaturen für HF-Modulbestückung führt zu zwei Fehlermechanismen:

ImAg-Anlaufen. Immersion Silver oxidiert bei erhöhter Temperatur in sauerstoffhaltiger Atmosphäre. Eine angelaufene ImAg-Oberfläche verliert Lötbarkeit; das Lot benetzt nicht mehr gleichmäßig, was zu offenen Lötstellen oder zu Lötflächen mit hohem Void-Anteil führt, obwohl die Pads vor dem Reflow sauber wirkten.

Oxidation des Lotpulvers. Die Partikel der Lotpaste entwickeln während der Aufheizrampe Oxidschichten, wenn Sauerstoff in der Ofenatmosphäre vorhanden ist. Diese Oxidschichten erhöhen die Viskosität des Lots im Reflow, verringern die Benetzungskraft und fördern Void-Bildung in allen Lötstellen, nicht nur unter Thermal Pads.

Die Reflow-Öfen von APTPCB für RO3003-HF-Module arbeiten mit reiner Stickstoffatmosphäre bei einem Restsauerstoffgehalt unter 500 ppm. Auf diesem Niveau ist die Oxidation der ImAg-Oberfläche über den gesamten Thermozyklus vernachlässigbar, und die Benetzung der Lotpaste ist deutlich besser als beim Luft-Reflow.

Reflow-Profil für hybride RO3003-Leiterplatten

| Phase | Zielwert | Randbedingung |

|---|---|---|

| Vorheizrampe | 1,5–2°C/Sekunde | Zu schnell: thermischer Schock für die FR-4/RO3003-Grenzfläche |

| Soak-Zone, Flussmittelaktivierung | 150–180°C, 60–90 Sekunden | Zu kurz: unvollständige Flussmittelaktivierung, Void-Bildung |

| Spitzentemperatur | 245–250°C | Maximal 260°C; niedrigere Spitze reduziert Stress an der PTFE/Kupfer-Grenzfläche |

| Zeit über Liquidus, 183°C | 30–45 Sekunden | Länger: mehr thermischer Stress; kürzer: unvollständige Koaleszenz |

| Abkühlrate | ≤3°C/Sekunde | Schneller: thermischer Schock für die Hybrid-Bondlinie |

Die Spitzentemperatur von 245–250°C liegt unter den 255–260°C, die auf FR-4-Linien üblich sind. Diese Reduzierung ist beabsichtigt: Das thermische Ausdehnungsverhalten von PTFE oberhalb von 250°C beginnt die Grenzfläche zwischen PTFE-Matrix und Kupferplattierung der Via-Zylinder zu belasten. Eine niedrigere Spitzentemperatur bei ausreichend Zeit über Liquidus für vollständige Lotkoaleszenz liefert daher eine bessere Langzeitzuverlässigkeit der Lötstellen auf RO3003-Substraten.

Mehrere Reflow-Durchgänge oberhalb von 220°C sollten nach Möglichkeit auf zwei begrenzt werden. Wenn Nacharbeit einen dritten Durchgang erfordert, sollte die bestückte Leiterplatte vor einer weiteren Nutzung auf Integrität der PTFE/FR-4-Grenzfläche geprüft werden.

Aspekte der Bauteilplatzierung bei HF-Transceivern

Planarität des Thermal Pads

QFN- und Chip-Scale-HF-ICs besitzen typischerweise ein freiliegendes Thermal Pad, das gleichmäßig Kontakt zum POFV-Lotdepot herstellen muss. Die Koplanarität des Bauteilgehauses, also die Höhenvariation der Anschlüsse über das Gehäuse hinweg, muss innerhalb der Höhe des Lotpastenauftrags liegen, damit das Thermal Pad die Paste konsistent berührt.

Vor dem Einschleusen in die Linie ist zu verifizieren, dass die Koplanarität des Bauteils innerhalb von 0,05mm liegt. Bauteile oberhalb dieser Schwelle verursachen ungleichmäßigen Kontakt am Thermal Pad und damit vorhersehbares Voiding an den höherliegenden Ecken, selbst wenn die Window-Pane-Schablone korrekt ausgelegt ist.

Feinpitch-Pads von HF-Steckverbindern

Viele HF-Module besitzen Edge-Launch-HF-Steckverbinder für den Testzugang. Diese liegen typischerweise bei 0,5mm Pitch oder kleiner. Auf RO3003-Leiterplatten mit ImAg-Oberfläche ist die Planarität des Finishs ein Vorteil: Die dünne, plane ImAg-Schicht verursacht nicht den Höhenversatz, den HASL erzeugen würde. Diese Feinpitch-Strukturen verlangen vor der Platzierung eine SPI-Prüfung des Pastendrucks, um Pastenvolumen und Lagegenauigkeit zu bestätigen, bevor irgendein Bauteil gesetzt wird.

Überlegungen zu Underfill für harsche Umgebungen

HF-Module für harte Umgebungen wie Fahrzeugaußenbereiche, Outdoor-Basisstationen oder luftgestützte Anwendungen erleben Vibrationspegel und thermische Schockraten, die die Ermüdungslebensdauer großer BGA-Lötstellen ohne Underfill überschreiten können. Werden auf RO3003-Leiterplatten BGA-Bauteile eingesetzt, muss bei der Auswahl des Underfill sowohl die Haftung auf der ImAg-Oberfläche als auch die Kompatibilität mit dem RO3003-Dielektrikum berücksichtigt werden, denn nicht jede Underfill-Formulierung benetzt PTFE-basierte Substrate ausreichend.

3D-Röntgeninspektion: Die einzige Möglichkeit, das Wichtige wirklich zu sehen

Was AOI übersieht

Nach dem Reflow fotografieren Standard-AOI-Systeme die Baugruppe von oben. Bei QFN-HF-Transceivern mit vollständig unter dem Gehäuse verborgenen Lötstellen, bei BGAs mit komplett eingeschlossenen Lotkugeln und bei freiliegenden Thermal Pads, die nur durch das Bauteil hindurch sichtbar sind, sieht AOI nichts Relevantes. Gerade die Bauteile, die auf einer hochfrequenten HF-Leiterplatte am wichtigsten sind, liegen außerhalb dessen, was AOI erkennen kann.

2D-Röntgen ist eine Verbesserung, reicht für POFV-Strukturen aber nicht aus: Eine 2D-Projektion legt die Via-Kupfersäulen, die darüberliegende Lötlage und die darunterliegenden Leiterplattenschichten in einem einzigen Bild übereinander. Die Void-Fläche innerhalb der Lötlage isoliert zu messen, ist damit nicht möglich.

3D-AXI mit Computertomographie

Die 3D-Automated-X-Ray-Inspection-Systeme von APTPCB rekonstruieren aus Mehrwinkelprojektionen ein hochauflösendes Volumenmodell. Qualitätsingenieure schneiden exakt durch die Ebene der Lötlage, isoliert vom Via-Kupfer darüber und den Leiterplattenschichten darunter, und messen:

- Gesamten aggregierten Void-Anteil über das gesamte Thermal Pad

- Abmessungen und Positionen einzelner Voids

- Nähe der Voids zu POFV-Via-Säulen

APTPCB-Akzeptanzkriterien für Voiding bei RO3003-Bestückung:

| Kriterium | IPC-A-610 Class 3 | APTPCB intern |

|---|---|---|

| Gesamtes Voiding auf dem Thermal Pad | ≤30% | ≤20% |

| Einzelner Void | Nicht spezifiziert | ≤5% der Pad-Fläche |

| Void über einer POFV-Thermal-Via | Nicht spezifiziert | Null-Toleranz |

Die Null-Toleranz für Voids über Thermal Vias steht nicht in IPC-A-610, sondern ist eine APTPCB-spezifische Forderung, die aus Thermalsimulationen abgeleitet wurde. Ein Void direkt über einer verfüllten Kupfer-Via-Säule unterbricht den primären Wärmepfad vom RFIC-Übergang zum Chassis. Das Ergebnis ist Betrieb oberhalb der maximalen Sperrschichttemperatur, erst mit allmählicher Gain-Kompression und schließlich mit Bauteilausfall. Kein Design-Margin kann einen unterbrochenen Wärmepfad kompensieren.

Erstmusterprüfung für RO3003-Bestückungsprogramme

Bevor Produktionsserien freigegeben werden, führt APTPCB bei RO3003-Bestückungsprogrammen eine Erstmusterprüfung durch. Die FAI für ein HF-Modul umfasst:

- 100 % 3D-AXI auf allen Bottom-Terminated-Components

- Mikroschliff eines repräsentativen Lötstellensatzes, Thermal Pad plus umliegende Anschluss-Pads

- Messung des thermischen Widerstands auf dem Wärmepfad des RFIC, sofern Testzugang vorhanden ist

- Dokumentation des Reflow-Profils für die konkrete Kombination aus Leiterplatte und Ofen

- SPI-Daten der Lotpaste aus dem ersten Produktionsdruckzyklus

Die FAI-Dokumentation bildet die Referenz, gegen welche die Stichproben aus Produktionslosen bewertet werden. Wenn der Void-Anteil in der Produktionsstichprobe ansteigt, zeigen die FAI-Daten, ob die Abweichung in der Schablonenleistung, im Pastenvolumen oder im Ofenprofil liegt, ohne dass die Ursachenanalyse jedes Mal von Grund auf neu beginnen muss.

Warum die Integration von Fertigung und Bestückung bei RO3003 wichtig ist

Die zuverlässigste Art, eine RO3003-Leiterplatte zu bestücken, besteht darin, Bestückung und Leiterplattenfertigung nicht voneinander zu trennen. Wenn nackte Leiterplattenfertigung und SMT-Bestückung vom selben Team in derselben Anlage durchgeführt werden:

- wird das Timing des Vorbake durch denselben Plan gesteuert, der auch die Linienauslastung steuert

- lässt sich die Lagerfähigkeit von ImAg mit direkter Kenntnis des Fertigungsdatums der Leiterplatte überwachen

- stehen dem Bestückungsingenieur, der die Schablonenöffnungen auslegt, die Planaritätsdaten der POFV-Oberflächen aus der Fertigung zur Verfügung

- fließen die 3D-AXI-Ergebnisse zum Voiding direkt als Prozessindikator an das Fertigungsteam zurück

Wenn Fertigung und Bestückung auf zwei Lieferanten aufgeteilt werden, zerfällt die Verantwortung für Voiding-Fehler: Der Bestücker schreibt sie der POFV-Planarität oder einer ImAg-Degradation während des Versands zu, der Leiterplattenfertiger verweist auf das Reflow-Profil. Haftung und Terminverzug bleiben beim OEM.

Der Turnkey-Service von APTPCB deckt die Fertigung von Rogers-RO3003-Leiterplatten bis hin zur SMT-Bestückung ab, mit gemeinsamer DFM-Dokumentation, gemeinsamer Lagerung vor Ort und einem einheitlichen IATF-16949-Qualitätsmanagementsystem für beide Prozessstufen.

Wenn Ihr Programm bereits unerwartetes Voiding in der Produktion gezeigt hat oder Sie das Schablonendesign vor dem ersten Prototypenlauf bewerten, ist der schnellste Diagnoseweg der Vergleich der 3D-AXI-Schnittdaten mit der FAI-Basislinie und der Abgleich mit den Zeitaufzeichnungen zwischen Vorbake und Reflow. Die meisten hartnäckigen Voiding-Probleme in RO3003-Programmen gehen auf eine von drei Variablen zurück: Drift im Intervall zwischen Vorbake und Reflow, Alter der ImAg-Oberfläche seit der Fertigung oder Schablonenverschleiß in der Serie. Kontaktieren Sie unser Bestückungsingenieurteam mit Ihren 3D-AXI-Daten, und wir können die Grundursache in der Regel identifizieren, bevor eine neue Schablone bestellt wird.

Referenzen

- SMT-Akzeptanz für Voids gemäß IPC-A-610 Acceptability of Electronic Assemblies, Class 3.

- Reflow-Profil- und Stickstoffatmosphärenvorgaben aus dem APTPCB High-Frequency SMT Assembly Control Plan (2026).

- Anforderungen an Feuchte-Vorbake gemäß IPC-1601 Printed Board Handling and Storage Guidelines.

- POFV-Anforderungen gemäß IPC-4761 Design Guide for Protection of Printed Board Via Structures.