Wenn ein HF-Ingenieur zum ersten Mal ein EM-Simulationstool mit RO3006 statt RO3003 oeffnet, wirken die Leiterbahnbreiten falsch. Ein 50Ω-Microstrip auf einem 10-mil-Core, der auf RO3003 10 mil breit waere, liegt auf RO3006 bei 5 bis 7 mil. Die Viertelwellenabschnitte sind kuerzer. Die Patchantenne ist kleiner. Alles, was mit der gefuehrten Wellenlaenge skaliert, ist um einen vorhersehbaren Faktor geschrumpft, und genau dieser Faktor macht RO3006 fuer bestimmte Designprobleme nuetzlich und fuer andere irrelevant.

Dieser Leitfaden richtet sich an HF-Ingenieure, die mit RO3006 arbeiten: wie die Uebertragungsleitungsgeometrie korrekt aufgesetzt wird, wie sich ein Insertion-Loss-Budget auf einem verluststaerkeren Substrat pro Inch aufbauen laesst, wie sich Via-Uebergaenge in einer kuerzeren Schaltung anders verhalten und welche Fertigungsrestriktionen die schmaleren Leiterbahnen fuer den Designprozess mitbringen.

Die Simulation fuer RO3006 korrekt aufsetzen

Die Substratparameter, die in eine HF-Simulation fuer RO3006 eingehen:

- Dk = 6,15 (verwenden Sie frequenzabhaengige Werte aus dem Rogers-MWI-2000-Rechner oder dem vollstaendigen Rogers-Datenblatt fuer Designs oberhalb von 20 GHz)

- Df = 0,0020 bei 10 GHz (auch hier fuer frequenzspezifische Werte das Rogers-Datenblatt heranziehen)

- Core-Dicke: gemaess dem konkreten Laminat, das bestellt wird. Bestaetigen Sie dies mit Ihrem Fertiger vor Simulationsbeginn, da Standard-RO3006-Dicken von den gewohnten RO3003-Dicken abweichen koennen

- Kupfergewicht und Folientyp: Low-Profile-ED-Kupfer (Ra ≈ 1,5 μm) fuer aeussere HF-Lagen, bei denen Leiterverluste zaehlen, und Standard-ED-Kupfer dort, wo nur DC- oder niederfrequente Signale gefuehrt werden

Verwenden Sie keine RO3003-Parameter fuer RO3006. Das klingt offensichtlich, doch aus frueheren Programmen uebernommene Simulationseinstellungen sind eine dokumentierte Ursache fuer erste Prototypen, deren Hardware nicht zum Modell passt. Verifizieren Sie die Substratdatei vor jeder S-Parameter-Simulation.

Ein wichtiger Prozesshinweis noch vor dem Layout: Der Aetzkompensationsfaktor fuer RO3006 muss spezifisch auf RO3006 charakterisiert sein. Ein Fertiger, der RO3003-kalibrierte Aetzkompensation auf Ihre 5 bis 7 mil breiten RO3006-Leiterbahnen anwendet, erzeugt systematische Impedanzfehler. Klaeren Sie dies vor der Gerber-Einreichung mit Ihrem Fertiger. Bei 6-mil-Leiterbahnen entspricht bereits 1 mil Aetzvariation einem Impedanzfehler von 17 %.

Uebertragungsleitungsgeometrie: Die Zahlen fuer Dk 6,15

Ungefaehre 50Ω-Microstrip-Leiterbahnbreiten fuer RO3006 (Dk = 6,15, 1 oz Kupfer) ueber gaengige Core-Dicken:

| Core Thickness | ~50Ω Trace Width on RO3006 | ~50Ω Trace Width on RO3003 | Reduction |

|---|---|---|---|

| 5 mil (0.127mm) | ~2–3 mil | ~4–5 mil | ~40% |

| 10 mil (0.254mm) | ~5–7 mil | ~9–11 mil | ~40% |

| 20 mil (0.508mm) | ~9–12 mil | ~18–22 mil | ~40% |

Die Reduktion um etwa 40 % bleibt ueber alle Core-Dicken hinweg erhalten, weil das Verhaeltnis von Leiterbahnbreite zu Hoehe fuer 50Ω-Microstrip primaer mit Dk skaliert. Fuer ein vorgegebenes Impedanzziel auf fester Core-Dicke erfordert ein hoeheres Dk eine schmalere Leiterbahn.

Diese Werte sind Startpunktschaetzungen aus analytischen Formeln erster Ordnung. Fuer die endgueltigen Leiterbahnbreiten in den Produktions-Gerbern gilt:

- Verwenden Sie Rogers MWI-2000 oder einen Full-Wave-EM-Solver mit den realen RO3006-Dk- und Core-Dickenwerten

- Fordern Sie vom Fertiger den Aetzkompensationsfaktor fuer Ihren konkreten Kupferfolientyp und das Kupfergewicht auf RO3006 an und bestaetigen Sie, dass er auf RO3006 charakterisiert wurde und nicht aus RO3003-Kalibrierdaten stammt

- Geben Sie ±10 % Impedanztoleranz in der Fertigungszeichnung an, inklusive TDR-Testcoupon-Verifikation auf jedem Produktionspanel

Bei einem 6-mil-Ziel auf einem 10-mil-Core entsprechen ±0,6 mil Aetzvariation bereits ±10 % der Leiterbahnbreite. Ein qualifizierter Fertiger erreicht das mit LDI-Prozessfaehigkeit; Standardbelichtung mit Phototool nicht.

Differentielle Paare und Masseebenen auf RO3006

Moderne RFICs fuer Radar-, 5G- und Kommunikationsanwendungen verwenden zunehmend differentielle HF-Ports. Auf RO3006 besteht ein 100Ω-Differentialpaar auf einem 10-mil-Core aus zwei etwa 4 bis 6 mil breiten Leiterbahnen mit 3 bis 5 mil Edge-to-Edge-Abstand, also so schmal, dass konstante Paarabstaende nur mit der Registriergenauigkeit von LDI einzuhalten sind.

Die engeren absoluten Abmessungen auf RO3006 machen die folgenden Regeln fuer Differentialpaare wichtiger als auf RO3003:

Durchgaengigkeit der Referenzebene ist Pflicht. Jeder Slot oder Void in der Referenzebene unter einem Differentialpaar vergroessert die Rueckstromschleifenflaeche und fuehrt einen Common-Mode-Rauschpfad ein. Bei schmaleren Leiterbahnen auf RO3006 konzentriert sich der Rueckstrom staerker direkt unter der Leiterbahn. Ein Slot unter dem Paar wirkt sich daher proportional staerker auf die differentielle Impedanz aus als derselbe Slot unter einem breiteren RO3003-Paar.

Rueckstrompfade an Vias. Bei jedem Differential-zu-Single-Ended-Uebergang per Via oder jedem Lagenwechsel-Via muessen benachbarte Masse-Rueckstrom-Vias innerhalb von etwa einer Leiterbahnteilung zum Signalvia platziert werden. Die engere Geometrie durch die schmaleren RO3006-Leiterbahnen reduziert den zulaessigen Abstand fuer die Rueckstrom-Massevias.

Insertion-Loss-Budget auf RO3006: Vom HF-Frontend rueckwaerts arbeiten

Jedes HF-PCB-Design beginnt mit einem Link Budget, also einer uebergeordneten Bilanz aus Signalgewinn und Signalverlust durch das System. Auf RO3006 ist der Substratverlustterm pro Laengeneinheit bei gegebener Frequenz etwa 2,9× hoeher als auf RO3003, dafuer sind die Schaltungen kuerzer. Um den tatsaechlichen Substratverlust durch einen konkreten Funktionsblock zu bestimmen, muss die Insertion-Loss-Rechnung auf die realen Abmessungen bezogen werden.

Beispiel: X-Band-Bandpassfilter (10 GHz) auf RO3006

Ein gekoppeltleitungsbasierter Bandpassfilter bei 10 GHz mit drei Resonatorsektionen auf RO3006 (Dk = 6,15) besitzt gekoppelte Leitungsabschnitte von etwa 4,0 mm pro Viertelwellenelement, verglichen mit etwa 5,3 mm auf RO3003. Drei gekoppelte Abschnitte ergeben rund 12 mm Gesamtlaenge, also 0,47 inch.

Dielektrischer Verlust bei 10 GHz auf RO3006: α_d ≈ 0,114 dB/inch

Dielektrischer Verlust im Filterkoerper: 0,47 inch × 0,114 dB/inch ≈ 0,054 dB (nur dielektrisch)

Das ist eine vereinfachte Schaetzung. Tatsaechliche Filterverluste umfassen zudem Leiterverluste, Diskontinuitaeten an Kopplungsstellen und Endeffekt-Korrekturen. Die Richtung ist dennoch eindeutig: Bei einem 10-GHz-Filter wird der Insertion Loss durch die Resonatorsektion selbst von anderen Effekten dominiert. Die Groessenreduktion auf RO3006 fuehrt im X-Band also nicht automatisch zu einer katastrophalen Verluststrafe.

Bei hoeheren Frequenzen steigt die Strafe jedoch: Bei 24 GHz liegt der dielektrische Verlust von RO3006 bei etwa 0,274 dB/inch gegenueber 0,095 dB/inch bei RO3003. In diesem Bereich haengt die Rechtfertigung fuer RO3006 viel staerker davon ab, ob die Groessenreduktion das Verlustbudget aufwiegt.

Surface Finish fuer RO3006 HF-PCBs

Im HF- und Mikrowellenbereich wirkt das Surface Finish der aeusseren Kupferlagen direkt im Leiterverlustbudget mit. Dieselbe Auswahl-Logik wie bei RO3003-HF-PCBs gilt auch fuer RO3006:

Immersion Silver (ImAg) ist fuer alle HF-Lagen oberhalb von 3 GHz zu bevorzugen. Die 0,1 bis 0,2 μm dicke Silberschicht ist elektromagnetisch transparent. Der HF-Strom fliesst auf der darunterliegenden Kupferoberflaeche. ImAg erhaelt den Verlustvorteil einer Low-Profile-Kupferfolienspezifikation. Lagerfaehigkeit in versiegelter Verpackung: 12 Monate; nach dem Oeffnen: innerhalb von 5 Arbeitstagen bestuecken.

ENIG fuegt eine 3 bis 5 μm dicke Nickelsperrschicht hinzu, deren spezifischer Widerstand etwa 4× hoeher als der von Kupfer ist. Bei 10 GHz fuehrt das zu messbar hoeherem Leiter-Insertion-Loss. Fuer RO3006-Designs im S-Band oder darunter, wo Leiterverluste weniger kritisch sind, kann die groessere Toleranz gegenueber laengeren Lagerzeiten ENIG bei Programmen mit unsicherem Bestueckungszeitpunkt attraktiver machen.

Ein Detail ist auf RO3006 wichtiger als auf RO3003: Da die HF-Leiterbahnen auf RO3006 schmaler sind, bildet der Anteil von ImAg oder ENIG am Leiterquerschnitt einen groesseren Prozentsatz des Gesamtleiters. Die Surface-Finish-Strafe beim Leiterverlust skaliert deshalb direkter mit der schmaleren Leiterbahngeometrie. Der Vorteil von ImAg gegenueber ENIG ist auf RO3006 bei gleicher Frequenz geringfuegig bedeutender als auf RO3003.

Via-Uebergaenge auf RO3006: Resonanzbetrachtungen

Bei jeder HF-Frequenz enthaelt ein durchkontaktiertes Via, das die aeussere HF-Lage mit einer inneren Referenzebene verbindet, einen Via-Stub unterhalb der zuletzt angeschlossenen Lage. Dieser Stub erzeugt bei seiner Viertelwellen-Resonanzfrequenz ein Uebertragungsminimum.

Auf RO3006 ist die gefuehrte Wellenlaenge bei jeder Frequenz kuerzer als auf RO3003, um etwa 25 bis 30 %. Das bedeutet:

Viertelwellen-Stubs sind auf RO3006 physisch kuerzer. Fuer eine gegebene physische Stub-Laenge liegt die Resonanzfrequenz in Luft auf RO3006 hoeher als auf RO3003, bleibt aber aehnlich, wenn das Dielektrikum den Stub ausfuellt. Die exakte Resonanzberechnung haengt von der dielektrischen Fuellung des Stub-Bereichs ab.

Via-Uebergaenge sind relativ zur gefuehrten Wellenlaenge groesser. Auf einem kuerzerwelligen Substrat macht eine gegebene Via-Geometrie, etwa 0,3 mm Via mit 0,3 mm Pad, einen groesseren Anteil der gefuehrten Wellenlaenge aus. Die parasitaere Induktivitaet des Via-Barrels, etwa 0,5 bis 1,0 nH fuer ein 0,3-mm-Via in einem 0,25-mm-Core, wird im Verhaeltnis zu den kuerzeren Schaltungsabmessungen auf RO3006 bedeutsamer.

Fuer HF-Programme, bei denen die Via-Uebergangsperformance relevant ist, oberhalb von etwa 5 bis 8 GHz auf RO3006, beseitigen Blind Vias von der aeusseren RO3006-Lage zur ersten inneren Referenzebene die Stub-Resonanz vollstaendig. Das Aspect-Ratio-Limit fuer IPC-Class-3-Blind-Vias auf PTFE liegt bei 0,8:1 (Durchmesser:Tiefe). Bei einem 10-mil-Core (0,254 mm) ergibt sich damit ein minimaler Blind-Via-Durchmesser von etwa 0,32 mm.

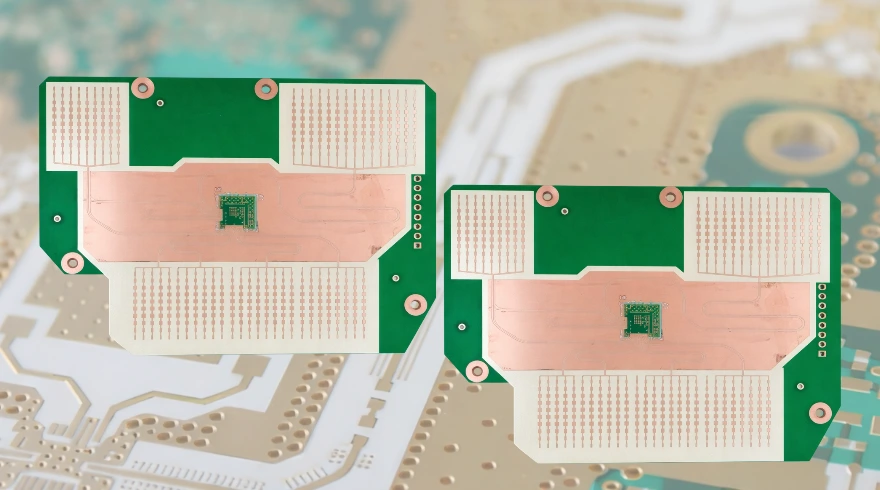

Hybrid-Stackup fuer RO3006 RF-PCBs

Bei Programmen, in denen die Kosten wichtig sind, setzt ein hybrider RO3006/FR-4-Stackup das RO3006-Material nur auf den aeusseren HF-Lagen ein und verwendet hoch-Tg-FR-4 fuer innere Verdrahtung und Stromverteilung. Die Kostensenkung ist proportional dazu, wie viel des Leiterplattenquerschnitts aus FR-4 statt aus RO3006 besteht. Dieselbe oekonomische Logik wie bei hybriden RO3003-Programmen gilt auch hier, und die RO3003-PCB-Kostenanalyse behandelt diese Rechnung im Detail.

Die kritische Designregel fuer hybride RO3006-Stackups, die restriktiver ist als bei hybriden RO3003-Aufbauten, lautet: Die Leiterbahnen auf den aeusseren RO3006-Lagen sind schmaler, und der Bonding Film an der RO3006/FR-4-Schnittstelle darf waehrend der Laminierung nicht in diese schmaleren Leiterbahnkanäle einfliessen. Low-Flow-Prepreg mit hohem Tg an der PTFE/FR-4-Schnittstelle ist zwingend erforderlich und nicht nur empfohlen. Ein Bonding Film, der 1 mil in eine 10-mil-RO3003-Leiterbahn fliesst, veraendert die effektive Leiterbahnbreite um 10 %. Derselbe Fluss in eine 6-mil-RO3006-Leiterbahn veraendert sie um 17 %.

Die DFM-Pruefung fuer hybride RO3006-Stackups sollte explizit kontrollieren:

- Bonding-Film-Spezifikation und dokumentierte Fliesseigenschaften

- Bow/Twist-Testdaten aus dem konkret vorgeschlagenen RO3006/FR-4-Stackup

- Bestaetigung der Leiterbahnbreite auf den RO3006-HF-Lagen nach der Laminierung und nicht nur auf Coupons vor der Laminierung

RF-PCB-Designreview vor der Fertigung

Bei RO3006-HF-PCBs eliminiert ein strukturiertes DFM-Review vor der Gerber-Einreichung die haeufigsten Probleme des ersten Prototyps. Das 24-Stunden-DFM-Review von APTPCB fuer RO3006-Programme prueft gezielt:

- Leiterbahnbreiten verifiziert gegen RO3006-Dk und reale Core-Dicke und nicht gegen auf RO3003 kalibrierte Werte

- Via-Aspect-Ratios fuer alle Blind Vias bestaetigt gegen das PTFE-IPC-Class-3-Limit von 0,8:1

- POFV-Kennzeichnung bei allen Bauteil-Footprints mit Thermal Pad

- Kupferdichte der inneren FR-4-Lagen ≥75 % bei Hybrid-Stackups, kritisch fuer Bow/Twist-Management

- Platzierung von TDR-Testcoupons auf dem Panel fuer die Impedanzverifikation in der Produktion

Die schmale Leiterbahngeometrie bei Dk 6,15 ist der Ursprung der meisten RO3006-Probleme beim ersten Prototyp, entweder durch Simulationen mit falschem Dk oder durch aus RO3003-Programmen uebernommene Aetzkompensationsfaktoren. Wer beides vor dem Bohren des Panels erkennt, spart einen kompletten Prototypenzyklus. Senden Sie Gerberdaten an das Engineering-Team von APTPCB, um den DFM-Prozess zu starten.