Smart-TV-Mainboards vereinen Applikationsverarbeitung, Videoskalierung und -verarbeitung, mehrere Hochgeschwindigkeitsschnittstellen wie HDMI, USB und Ethernet, drahtlose Konnektivitaet sowie Audiosysteme auf Leiterplatten, die sehr aggressive Kostenziele einhalten und zugleich ein hochwertiges Seherlebnis liefern muessen. Die PCB-Herausforderungen reichen von extrem schnellen HDMI-2.1-Schnittstellen mit 48 Gbit/s Gesamtdatenrate bis hin zu grossflaechigen Panelinterfaces und der Einbindung der Stromversorgung.

Dieser Leitfaden konzentriert sich auf die PCB-spezifischen Aspekte des Smart-TV-Designs: die Aufteilung zwischen Mainboard und T-CON, die Routing-Anforderungen von Video-SoCs, die Signalintegritaet von HDMI 2.1, das Design der Panelschnittstelle, die Architektur der Stromversorgung sowie das fuer Fernsehprodukte entscheidende Spannungsfeld zwischen Qualitaet und Kostenoptimierung in der Fertigung.

Design Checklist (Fast Pass)

- Frueh partitionieren: Mainboard vs. T-CON vs. PSU-Board festlegen und Interconnect- sowie Steckverbinderwahl frueh einfrieren.

- HDMI nah platzieren: HDMI-2.1-FRL-Strecken kurz halten; Footprints fuer ESD, CMC und Retimer von Anfang an einplanen.

- DDR als Gesamtsystem betrachten: Stackup, Impedanz, Laengenabgleich, Referenzflaechen und Rueckstrompfade zusammen auslegen.

- PDN und Thermik gemeinsam entwickeln: Kupfer, Via-Arrays und die Waermeverteilung ueber das Chassis gehoeren zum eigentlichen Stromversorgungsdesign.

- DFM auf Kosten trimmen: HDI nur dort einsetzen, wo es wirklich noetig ist; Panelnutzung und Testzugang optimieren.

In This Guide

- TV-Board-Architektur: Aufteilung zwischen Mainboard und T-CON

- Routing-Anforderungen fuer den Video-Processing-SoC

- Umsetzung der High-Speed-Schnittstelle HDMI 2.1

- Design der Panel-Timing-Schnittstelle

- Integration der Stromversorgung und thermische Aspekte

- Kostenoptimierte Fertigung fuer Fernsehprodukte

TV Board Architecture: Main Board and T-CON Partitioning

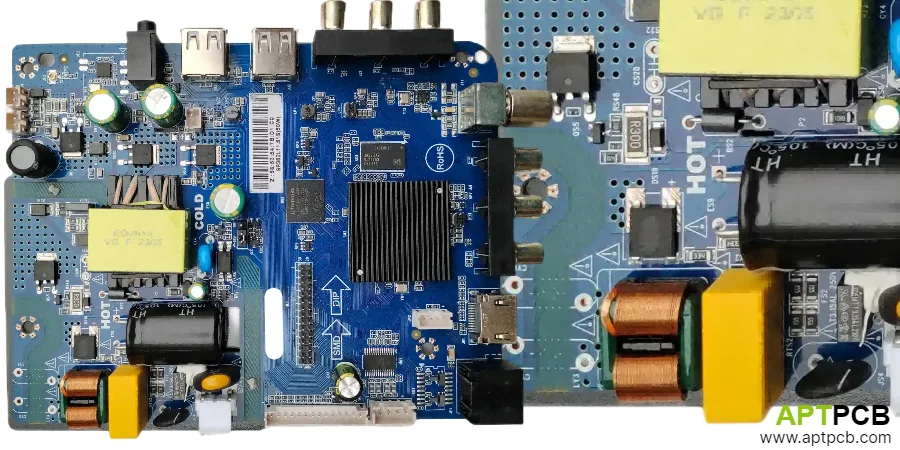

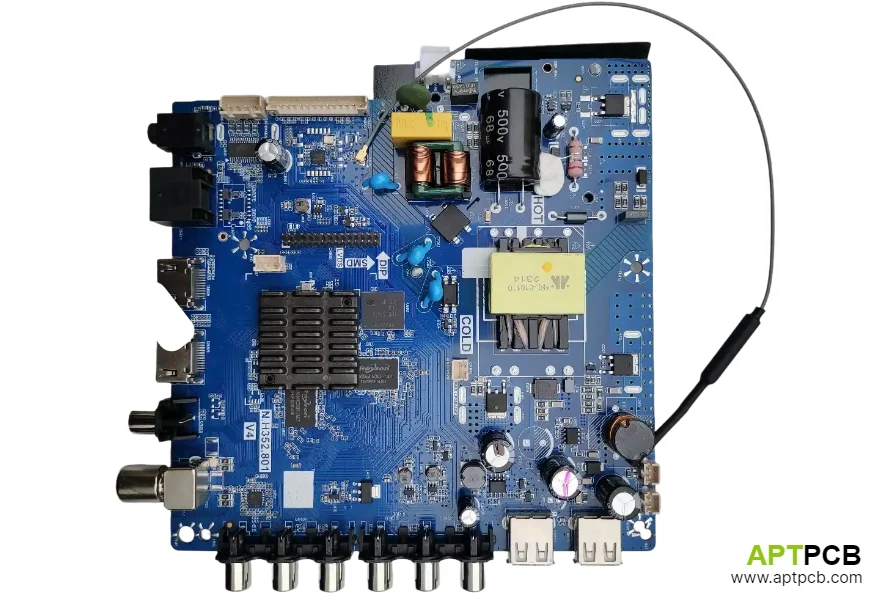

Die Elektronik eines Smart TVs verteilt sich in der Regel auf mehrere PCBs: Das Mainboard uebernimmt Applikationsverarbeitung, Konnektivitaet sowie Videoeingang und -verarbeitung; das T-CON-Board steuert das Panel und optimiert die Bilddarstellung; und das Netzteilboard stellt mehrere Versorgungsschienen bereit. Diese Aufteilung ergibt sich sowohl aus funktionalen Anforderungen als auch aus der Lieferkette, denn verschiedene Panels verwenden unterschiedliche T-CON-Designs, waehrend Mainboards oft produktlinienuebergreifend standardisiert werden.

Die Schnittstelle zwischen Mainboard und T-CON uebertraegt bereits voll aufbereitete Videodaten mit Aufloesungen bis 8K. Dafuer sind entweder extrem bandbreitenstarke parallele Schnittstellen erforderlich, bei LVDS also Dutzende differenzieller Paare, oder serielle Protokolle wie V-by-One oder eDP, die die Leiteranzahl reduzieren, dafuer aber Multi-Gigabit-Signalintegritaet verlangen. Diese Board-zu-Board-Schnittstelle bestimmt haeufig die obere Leistungsgrenze des Videosystems.

Board Partitioning Considerations

- Umfang des Mainboards: SoC, Speicher, HDMI-Receiver, USB- und Ethernet-Schnittstellen, WiFi- und Bluetooth-Module, Audioverarbeitung sowie Anbindungen an T-CON und Power-Boards.

- Integrationsgrad des T-CON: Manche Panels integrieren den T-CON direkt in das Panel, andere verwenden ein separates T-CON-Board. Das beeinflusst die Interface-Anforderungen des Mainboards direkt.

- Schnittstellenwahl: Die Panelspezifikation gibt die Richtung vor. Viele 4K60-Designs nutzen V-by-One HS mit etwa 8 Lanes in der Klasse von etwa 3 bis 4 Gbit/s pro Lane; 8K benoetigt meist mehr Lanes, hoehere Datenraten oder ein anderes Interface.

- Steckverbindertypen: High-Speed-Interfaces erfordern spezialisierte Steckverbinder mit kontrollierter Impedanz. Flachbandkabel begrenzen die Bandbreite und muessen sehr sorgfaeltig ausgelegt werden.

- Stromverteilung: Das Mainboard kann die T-CON mitversorgen, was die Stromtragfaehigkeit auf dem Mainboard erhoeht, oder die T-CON erhaelt die Versorgung direkt vom Netzteilboard.

- Mechanische Anordnung: Das Mainboard sitzt typischerweise unten auf der Rueckseite des Bildschirms; thermische Randbedingungen verlangen Abstand zum Panel und ausreichend Luftpfade.

Das Verstaendnis dieser Systemarchitektur steuert die PCB-Partitionierung und beeinflusst damit sowohl die elektrische Performance als auch die Fertigungseffizienz.

Video Processing SoC Routing Requirements

Smart-TV-SoCs integrieren ein erhebliches Mass an Komplexitaet: Quad-Core- oder Octa-Core-Applikationsprozessoren, dedizierte Videodecoder fuer mehrere Codecs in 4K- oder 8K-Aufloesung, Display-Engines mit Skalierung und Bildverbesserung sowie zahlreiche Schnittstellen. Diese stark integrierten Bausteine sitzen in grossen BGA-Gehaeusen mit oft 500 bis weit ueber 1000 Pins und feinem Pitch von 0,4 bis 0,65 mm. Das Routing muss deshalb Leistung und Herstellbarkeit zugleich absichern.

Besonders anspruchsvoll sind die Speicherinterfaces. DDR4 oder LPDDR4/5 arbeiten mit Datenraten, die sauberen Laengenabgleich und kontrollierte Impedanzen erfordern. Anders als bei Smartphones, wo Speicher oft im Package-on-Package sitzt, verwenden TV-SoCs ueblicherweise diskreten Speicher, sodass das komplette Interface auf Leiterplattenebene geroutet werden muss.

SoC Routing Guidelines

- BGA-Fanout-Strategie: Fine-Pitch-BGAs brauchen Via-in-Pad oder Dog-Bone-Fanout; Durchkontaktierungen begrenzen die verfuegbaren Routingkanaele, daher koennen Blindvias bei dichten Packages sinnvoll sein.

- Speicher-Routing: DDR4 bei 2666 bis 3200 MT/s verlangt Laengenabgleich innerhalb der Byte-Lanes von etwa ±5 mm, DQS-zu-DQ-Abgleich von etwa ±10 mm sowie konsistente Impedanzen.

- Anforderungen an Referenzflaechen: Speicher- und High-Speed-Signale brauchen durchgehende Referenzflaechen; Strombahnen oder Vias in den Referenzebenen unter kritischen Signalen sind zu vermeiden.

- Entkopplungsstrategie: Die Versorgungspins des SoC benoetigen lokale Entkopplung, etwa 100 nF an jedem Pin-Cluster, plus groessere Bulk-Kapazitaeten von 10 bis 100 uF in der Naehe. Die Bauteile muessen so nah an die Pins wie das Routing es zulaesst.

- JTAG- und Debug-Zugang: Debug-Schnittstellen wie JTAG oder UART muessen fuer Entwicklung und Produktionstests erreichbar bleiben; Testpunkte oder Header sind entsprechend zu positionieren.

- Thermisches Design: Die Verlustleistung des SoC, typischerweise 5 bis 15 W, erfordert Thermovias unter dem Package und ausreichend Kupferanbindung zu Kuehlkoerper- oder Chassis-Kontaktstellen.

Das Routing von Video-SoCs profitiert von High-Speed-PCB-Designmethoden, damit Speicher- und Displayschnittstellen ihre noetigen Leistungsreserven erreichen.

HDMI 2.1 High-Speed Interface Implementation

HDMI 2.1 gehoert zu den anspruchsvollsten Consumer-Interfaces ueberhaupt. Mit 12 Gbit/s pro Lane ueber vier Datenlanes, also insgesamt 48 Gbit/s, lassen sich 8K bei 60 Hz oder 4K bei 120 Hz mit HDR uebertragen. Das Routing zwischen HDMI-Receiver-IC und Stecker muss die Signalintegritaet in einem Frequenzbereich bewahren, in dem die Wellenlaengen bereits in die Groessenordnung der Leiterbahnlaengen fallen. Entsprechend ist diszipliniertes Transmission-Line-Design Pflicht.

Aeltere HDMI-1.4- und 2.0-Varianten mit bis zu 18 Gbit/s Gesamtbandbreite arbeiteten mit source-terminierter Differenzsignalisierung und moderater Impedanztoleranz. HDMI 2.1 FRL, Fixed Rate Link, setzt deutlich hoehere Massstaebe: 100 Ohm differentielle Impedanz (±10%), eng abgestimmte Laengen innerhalb jedes differentiellen Paares und eine saubere Kontrolle von Insertion Loss und Return Loss ueber den gesamten Kanal aus Stecker, PCB und Kabel.

HDMI 2.1 Routing Requirements

- Impedanzkontrolle: 100 Ohm differentielle Impedanz ±10%; eng gekoppelte differenzielle Paare reduzieren EMI und erhalten die Gleichtaktunterdrueckung.

- Kanalverlust: Bei 12 Gbit/s pro Lane ist die Verlustreserve schnell aufgebraucht. Leiterbahnen sollten kurz bleiben; wenn das nicht moeglich ist, sind Low-Loss-Laminate und/oder Redriver oder Retimer zu pruefen.

- Laengenbegrenzung: HDMI-Leiterbahnen so kurz wie praktikabel halten; unter 50 mm werden Verluste und Skew am besten begrenzt, weshalb die Platzierung des Steckverbinders nahe am Receiver-IC wichtig ist.

- Lagenwahl: HDMI am besten auf Lagen direkt neben massiven Ground-Planes routen; Microstrip auf Aussenlagen ist moeglich, wenn EMI im Griff bleibt, Stripline bietet die bessere Abschirmung.

- Via-Uebergaenge: Lagenwechsel moeglichst vermeiden. Wenn sie unvermeidlich sind, Stub-Laengen minimieren, etwa durch Backdrilling wo sinnvoll, und Referenzflaechen durchgaengig halten.

- ESD-Schutz: HDMI-Ports brauchen ESD-Schutz. Die Platzierung beeinflusst die Signalintegritaet direkt; daher TVS-Dioden mit geringer Kapazitaet unter 0,3 pF direkt am Stecker einsetzen.

Fuer HDMI 2.1 kann eine Signalintegritaetssimulation erforderlich sein, um die Einhaltung der Margen zu bestaetigen, besonders bei laengeren Strecken oder bei Einsatz von Standard-FR-4.

Panel Timing Interface Design

Die Schnittstelle zwischen Mainboard oder T-CON und LCD- beziehungsweise OLED-Panel transportiert Videodaten mit Datenraten, die Pixelclock und Farbtiefe entsprechen. Ein 4K-Panel mit 60 Hz und 10-Bit-Farbe benoetigt ungefaehr 17 Gbit/s Videodaten, uebertragen ueber LVDS, V-by-One oder proprietaere Schnittstellen abhaengig von Panelhersteller und Aufloesung.

V-by-One HS dominiert aktuelle 4K-TV-Implementierungen. Gegenueber LVDS werden weniger Lanes benoetigt, typischerweise 8 Paare statt 16 bis 32 Paare, dafuer aber mit hoeheren Datenraten von typischerweise 3,6 bis 4,0 Gbit/s pro Lane. Die geringere Lane-Zahl vereinfacht das Routing, verschaerft aber die Anforderungen an die Signalintegritaet jeder einzelnen Lane. Flexkabel zum Panel bringen zusaetzliche Impedanzspruenge ein, die ueber Steckverbinderwahl und Terminierungsdesign auf dem PCB sauber beherrscht werden muessen.

Panel Interface Implementation

- Protokollwahl: Die Panelspezifikation bestimmt das Interface. V-by-One HS ist bei den meisten 4K-Panels ueblich; LVDS bleibt bei niedrigeren Aufloesungen verbreitet; einige 8K-Panels nutzen proprietaere High-Speed-Schnittstellen.

- Lane-Konfiguration: V-by-One HS verwendet typischerweise 8 Lanes fuer 4K 60 Hz bei 10 Bit; die Zahl skaliert mit Aufloesung, Bildwiederholrate und Farbtiefe.

- Steckverbinder-Interface: Panelsteckverbinder muessen die Impedanz halten; das Flexkabel zwischen Board und Panel fuehrt Verluste und Skew ein, die die maximal erreichbare Bitrate beeinflussen.

- Referenztakt: Panelinterfaces benoetigen stabile Referenztakte. Die Wahl von Quarz oder Oszillator, die Filterung der Versorgung und die Routing-Isolation wirken direkt auf den Clock-Jitter.

- Terminierungsdesign: Bei V-by-One-Empfaengern ist On-Chip-Terminierung ueblich; die Terminierungsanforderungen des Panel-Eingangs und die Ausgangsimpedanz der Quelle muessen trotzdem geprueft und aufeinander abgestimmt werden.

- EMI-Aspekte: Panelsignale koennen ueber Flexkabel abstrahlen; saubere Steckverbindererdung, Kabelschirmung und Abstand zu empfindlichen Schaltungen reduzieren die EMI-Belastung.

Das Design der Panelschnittstelle erfordert enge Abstimmung mit dem Panelanbieter, um Timing, Spannungspegel und Steckverbinderkompatibilitaet zu verifizieren.

Power Supply Integration and Thermal Considerations

Smart-TV-Mainboards erhalten typischerweise 5 V oder 12 V vom Netzteilboard und erzeugen lokal die benoetigten Versorgungsschienen fuer den SoC, meist 0,9 bis 1,1 V fuer den Kern plus I/O-Spannungen, fuer den Speicher, etwa 1,2 V bei DDR4 oder LPDDR4, und fuer weitere I/O-Systeme. Das Power Delivery Network muss die transienten Stromspitzen des SoC abfangen und dabei die Spannung innerhalb enger Toleranzen halten, in der Regel ±3 % auf den Core-Rails.

Das Thermomanagement eines TV-Mainboards unterscheidet sich von tragbaren Geraeten. Die groessere Flaeche des Boards hilft beim Heat-Spreading, doch ein geschlossenes Gehaeuse und der Wunsch nach luefterlosem Betrieb begrenzen die Kuehlung. Das PCB fungiert daher gleichzeitig als Montagesubstrat und als primaerer Heat-Spreader, waehrend die Waerme ueber Thermal Interface Materials an das Metallchassis abgefuehrt wird.

Power and Thermal Design

- Wirkungsgrad der DC-DC-Wandler: Mehrphasige Buck-Wandler fuer den SoC erreichen ueber 90 % Wirkungsgrad; die Auswahl von Induktivitaeten und MOSFETs beeinflusst sowohl Effizienz als auch Temperaturverhalten.

- Spannungssequenzierung: Der SoC verlangt eine definierte Einschaltreihenfolge, typischerweise Core, dann I/O, dann Speicher. Ein Sequencing-Controller oder integrierter PMIC stellt das korrekte Timing sicher.

- Entkopplungsnetzwerk: Das SoC-PDN braucht Bulk-Kapazitaeten wie MLCC, Polymer- oder Elektrolytkondensatoren sowie Mittel- und Hochfrequenzkeramiken, die ueber das Netzwerk verteilt werden.

- Kupferflaechen: Kupferflaechen auf inneren Lagen unter SoC und Leistungsstufen maximieren; 1 oz oder 2 oz Kupfer auf Power-Layern verbessert sowohl Stromtragfaehigkeit als auch Waermeverteilung.

- Thermovia-Arrays: Dichte Via-Arrays unter SoC und MOSFETs der Leistungsstufe leiten Waerme auf Innenlagen und Rueckseite; gefuellte Vias verhindern das Abziehen von Lot in der Montage.

- Kuehlkoerper-Schnittstelle: Thermopad-Zonen des Mainboards koppeln ueber Thermal Interface Materials an das Chassis; flaechiges Kupfer liefert eine gleichmaessige thermische Anbindung, Via-Erhebungen in der Kontaktzone sind zu vermeiden.

Die Wechselwirkung zwischen Stromversorgung und Thermik verlangt ein solides Verstaendnis sowohl von Leistungselektronik als auch von Thermomanagement-Strategien fuer Consumer-Elektronik.

Cost-Optimized Manufacturing for Television Products

Fernsehprodukte stehen unter extremem Kostendruck. Kunden erwarten grossformatige 4K-TVs zu Preisen, die eine konsequente Kostenoptimierung ueber das gesamte Design hinweg erzwingen. PCB-Kosten tragen spuerbar zur gesamten Stueckliste bei, weshalb Materialwahl, Lagenanzahl und Panelausnutzung zentrale Designparameter sind. Die Qualitaet darf dabei nicht leiden, denn Garantiekosten aus Feldausfaellen uebersteigen Fertigungseinsparungen sehr schnell.

Die Balance zwischen Kosten und Qualitaet erfordert sorgfaeltige Entscheidungen: Standardmaterialien dort einsetzen, wo sie ausreichen, die Lagenzahl minimieren, ohne Funktionen zu verlieren, den Board-Umriss fuer gute Panelausnutzung optimieren und auf Fertigungsausbeute hin entwickeln. Eine fruehe Einbindung des Fertigungspartners hilft, Kostensenkungspotenziale zu finden, ohne die Qualitaet zu untergraben.

Cost Optimization Strategies

- Materialwahl: Standard-FR-4 mit Tg 140 bis 150 °C reicht fuer die meisten TV-Anwendungen; High-Speed-Materialien nur dort, wo HDMI 2.1 oder andere kritische Interfaces es wirklich verlangen.

- Lagenzahl minimieren: Ein 6-Lagen-Aufbau passt fuer viele TV-Mainboards; 4 Lagen sind bei weniger komplexen Designs mit sehr sauberer Routing-Optimierung moeglich.

- Panelausnutzung: Rechteckige Boards mit standardisierten Abmessungen nutzen das Fertigungspanel besser; Sonderformen senken die Ausnutzung und treiben die Kosten pro Platine.

- Via-Optimierung: Durchkontaktierungen sind deutlich guenstiger als Blind- oder Buried-Vias; wo immer moeglich fuer Through-Hole auslegen und HDI-Strukturen fuer wirklich notwendige Fine-Pitch-Bereiche reservieren.

- Oberflaechenfinish: HASL bleibt die guenstigste Option fuer Through-Hole- und grossrastrige Bauteile; ENIG bietet eine plane Oberflaeche fuer Fine-Pitch, kostet aber mehr.

- Testabdeckung: Design for Test mit gut erreichbaren Testpunkten senkt Fixture-Kosten und verbessert die Fehlererkennung; Flying-Probe-Tests eignen sich fuer mittlere Stueckzahlen.

Partnerschaften in der Serienfertigung von Leiterplatten schaffen Spielraum fuer Kostenoptimierung ueber Prozesseffizienz und Volumenpreise, ohne die Qualitaetskontrolle aufzugeben.

Technical Summary

Das Smart-TV-PCB-Design muss fortgeschrittene Anforderungen an die Signalintegritaet, etwa fuer HDMI 2.1 und schnelle Panelinterfaces, mit den harten Kostenzielen von Consumer-TV-Produkten in Einklang bringen. Erfolg entsteht durch saubere Architekturentscheidungen, also Board-Partitionierung, Interface-Wahl und Materialspezifikation, die die Zielperformance erreichen und gleichzeitig die Gesamtsystemkosten kontrollieren.

Zu den entscheidenden Technikpunkten gehoeren die HDMI-Umsetzungsstrategie mit Blick auf Leiterbahnlaengen, Materialwahl und EMI-Management, die Kompatibilitaet der Panelschnittstelle samt Protokoll- und Steckerwahl, die Architektur der Stromversorgung in Bezug auf Effizienz und Transientenverhalten sowie die thermische Loesung, bei der das PCB selbst Teil des Kuehlkonzepts ist.

Bei der Wahl des Fertigungspartners muessen technische Faehigkeiten wie High-Speed-Routing und Multilayer-Qualitaet ebenso bewertet werden wie Kostenwettbewerbsfaehigkeit. Die fuer TVs typischen Volumina rechtfertigen oft Optimierungen, die bei kleineren Produkten nicht moeglich sind. Trotz Kostenfokus bleiben robuste Qualitaetssysteme unverzichtbar, weil Garantiekosten durch Fertigungsfehler Produktionsersparnisse schnell uebersteigen.