Im Zentrum jedes 77-GHz-Radar-Fertigungsprogramms steht ein Paradox: Das Substrat, das gezielt wegen seiner HF-Leistung ausgewählt wurde, ist thermisch isolierend. Die dielektrischen Eigenschaften von Rogers RO3003 sind hervorragend. Seine Wärmeleitfähigkeit liegt jedoch bei 0,50 W/m/K und damit eher in einem Bereich, der verglichen mit den Anforderungen unter einem mit voller Leistung betriebenen Radar-Transceiver-IC fast an Konstruktionsschaum erinnert.

Das ist kein Grund, RO3003 zu vermeiden. Es ist ein Grund, genau zu verstehen, was der Fertigungsprozess dagegen tun muss. Dieser Prozess beginnt bereits upstream: Die PTFE-Fertigungsschritte, mit denen das Bare Board entsteht, also angepasste Bohrparameter, Vakuum-Plasma-Desmear und kontrollierte Kühlung bei Hybridlamination, entscheiden darüber, ob die POFV-Thermal-Via-Arrays und Kupferstrukturen für das Wärmemanagement noch vor der Bestückung spezifikationsgerecht aufgebaut werden.

Das thermische Paradox verstehen

Ein 77-GHz-RFIC-Verstärker, der ein Phased-Array-Radar treibt, kann mehrere Watt in ein Package-Thermal-Pad abführen, das kleiner als eine Briefmarke ist. Auf einer Standard-FR-4-Leiterplatte würde sich diese Energie seitlich durch das Substrat ausbreiten, ineffizient, aber zumindest teilweise. Bei RO3003 mit 0,50 W/m/K findet seitliche Wärmeverteilung praktisch nicht statt. Die Wärme staut sich direkt unter dem Bauteil.

Die nachgelagerten Folgen:

Gain Compression: Wenn sich die Sperrschichttemperatur dem Maximalwert des RFIC nähert, bei Automotive-Bauteilen typischerweise 125 bis 150 °C, komprimiert die Verstärkung des Verstärkers. Die Ausgangsleistung sinkt. In einem 77-GHz-Kollisionsvermeidungssystem bedeutet das geringere Erkennungsreichweite.

Phasenverschiebung: Obwohl der TcDk-Wert von RO3003 mit −3 ppm/°C ausgezeichnet ist, führen extreme lokale Temperaturen oberhalb von etwa 120 °C zu volumetrischer Ausdehnung in Z-Richtung im umgebenden Dielektrikum. Dadurch verschiebt sich die verteilte Kapazität benachbarter Antennen-Feed-Leitungen, und es entsteht Phasenrauschen, das die Beam-Steering-Genauigkeit verschlechtert.

Lötstellen-Ermüdung: Temperaturgradienten zwischen 120 °C an der Sperrschicht und 40 °C Umgebungstemperatur in nur 5 mm Abstand erzeugen zyklische mechanische Scherkräfte auf den Lötstellen. Über Tausende thermische Zyklen entwickeln sich Ermüdungsrisse.

Die technische Lösung besteht darin, vor der Bestückung einen leitfähigen thermischen Pfad durch das Substrat zu entwerfen. Dieser Pfad wird aus galvanisch abgeschiedenem Kupfer mit 398 W/m/K aufgebaut und verläuft vertikal durch die Leiterplatte.

POFV-Thermal-Via-Arrays: den Wärmepfad in Z-Richtung auslegen

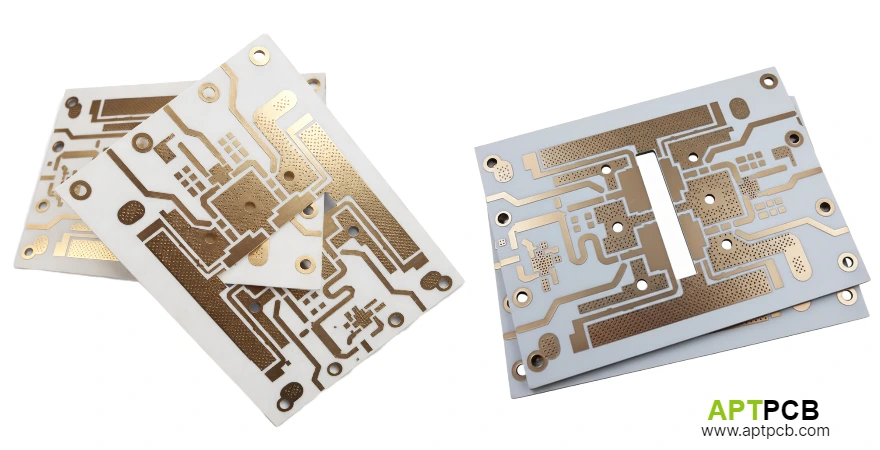

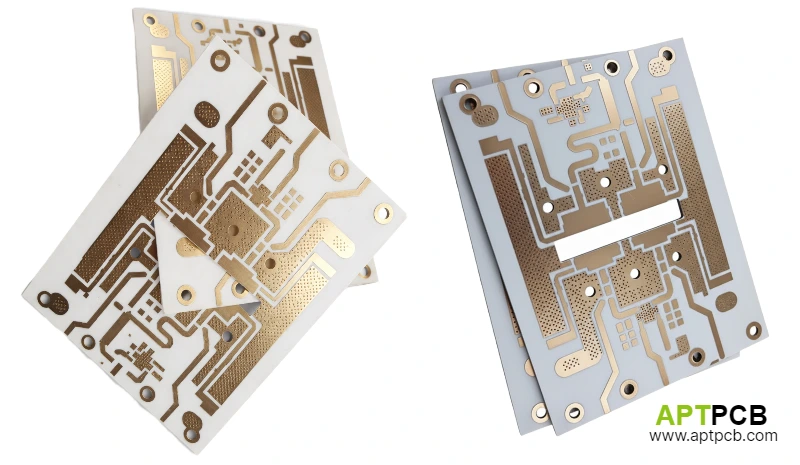

Der Standardansatz für RO3003-Radarboards ist ein Plated Over Filled Via (POFV)-Array, das direkt unter dem freiliegenden Thermal-Pad des RF-IC positioniert wird.

Der Mechanismus: Ein dichtes Array kupferplattierter Durchkontaktierungen bildet eine vertikale Kupfersäule vom Bauteilpad durch den RO3003-Kern bis in ein Metallchassis, eine Kaltplatte oder eine interne Wärmesenkschicht. Jeder Kupfer-Barrel eines Vias leitet Wärme etwa 800-mal effizienter als das umgebende Dielektrikum. Ein gut ausgelegtes Array reduziert den thermischen Widerstand unter einem hochleistenden RFIC je nach Array-Dichte und Chassis-Anbindung von mehreren hundert °C/W bei reinem Dielektrikumpfad auf 15 bis 25 °C/W.

Anforderung an Füllung und Planarisierung: Ein hohles Via lässt sich nicht zuverlässig überlöten. Lötpaste, die in ein ungefülltes Via einsackt, erzeugt einen Hohlraum unter dem Thermal-Pad, blockiert damit den Wärmepfad und schafft einen lokalen Hotspot. Die Gegenmaßnahme ist das Füllen der Via-Bohrungen mit wärmeleitendem Epoxidharz und anschließendes Überplattieren der gefüllten Oberfläche mit Kupfer, also POFV, sodass ein flaches, lötbares Pad entsteht. APTPCB zielt auf eine Oberflächenplanarität von POFV innerhalb von ±10 μm gegenüber dem umgebenden Kupfer. Größere Abweichungen führen zu ungleichmäßiger Pastenverteilung und damit zu Voiding, selbst bei gutem Stencil-Design.

Typische Dimensionierung für 77-GHz-Anwendungen: Für einen QFN-Transceiver mit 3×3 mm großem Thermal-Pad liefert ein 3×3- oder 4×4-Array aus 0,3 mm gebohrten Vias mit 0,6 mm Pitch von Mittelpunkt zu Mittelpunkt einen ausreichenden thermischen Widerstand. Die Via-Array-Abdeckung sollte mindestens 50 % der Thermal-Pad-Fläche betragen. Vor Abschluss des Layouts ist eine thermische Simulation erforderlich. Via-Geometrie, Füllspezifikation und Planarität des Cap-Plating gehören zu den fertigungskritischen Entscheidungen, die im Design- und DFM-Prozess für kundenspezifische RO3003-PCBs vertieft behandelt werden.

Oberflächenfinish: Immersionssilber vs. ENIG bei Millimeterwellen

Bei 77 GHz konzentriert der Skin-Effekt den Strom in den äußersten 1 bis 2 μm des Leiters. Das Oberflächenfinish ist damit Teil des HF-Signalpfads.

Immersionssilber (ImAg): Bei einer Schichtdicke von 0,1 bis 0,2 μm ist ImAg elektromagnetisch praktisch transparent. Der HF-Strom fließt auf der darunterliegenden Kupferoberfläche. Die Lötbarkeit ist ausgezeichnet, und die flache, glatte Morphologie erhält die Leitungsimpedanz entlang der RF-Feed-Leiterbahnen.

ENIG: Hier werden 3 bis 5 μm Nickel unter einer dünnen Goldschicht abgeschieden. Der spezifische Widerstand von Nickel ist etwa viermal höher als der von Kupfer. Bei 77 GHz verursacht diese Schicht im Vergleich zu ImAg etwa 0,1 bis 0,2 dB/Zoll zusätzlichen Einfügeverlust. Bei einem 3 Zoll langen Antennen-Feed-Netzwerk ist dieser Nachteil messbar und real.

Handhabungsfolgen von ImAg: Silber läuft bei Kontakt mit Schwefelverbindungen oder Fingerölen an. APTPCB liefert alle RO3003-Boards mit ImAg-Finish in schwefelfreiem Schutzpapier und vakuumversiegelt in Moisture Barrier Bags mit Trocknungsmittel und Humidity Indicator Cards aus. Versiegelte Lagerfähigkeit: 12 Monate. Nach dem Öffnen: Bestückung innerhalb von 5 Arbeitstagen.

SMT-Bestückung: vier Kontrollen, die über Zuverlässigkeit entscheiden

Die vier folgenden Kontrollen adressieren die Fehlermodi, die bei hybriden RO3003-Boards auf SMT-Ebene spezifisch auftreten. Für Programme, die eine vollständige Prozessreferenz benötigen, einschließlich First Article Inspection, Anforderungen an die Bauteil-Koplanarität und den vollständigen 3D-AXI-Akzeptanzkriterien für Voids, behandelt der Leitfaden zum RO3003-PCB-Assembly-Prozess jeden Schritt von Pre-Bake bis Post-Reflow-Validierung.

1. Feuchte-Pre-Bake vor dem Linieneinlauf

RO3003 nimmt nahezu keine Feuchtigkeit auf, nur 0,04 %. Doch die in kommerziellen 77-GHz-Programmen üblichen Hybrid-RO3003/FR-4-Boards enthalten hygroskopische innere FR-4-Lagen. Feuchtigkeit, die während eines 250-°C-Reflow-Zyklus bis zur Grenzfläche zwischen Dielektrikum und Kupfer gelangt, kann schlagartig zu Dampf werden und interne Delamination sowie Via-Barrel-Risse verursachen.

APTPCB führt unmittelbar vor Beginn der SMT-Bestückungsservices bei allen Hybridboards ein kontrolliertes Pre-Bake durch. Dieser Backzyklus treibt aufgenommene Feuchte aus den FR-4-Lagen aus, ohne das ImAg-Finish übermäßig zu oxidieren. Die Boards gelangen innerhalb weniger Minuten nach Abschluss des Bake-Zyklus in die SMT-Linie.

2. Window-Pane-Stencil-Design für Thermal-Pads

Dies ist das Detail, das am häufigsten darüber entscheidet, ob das Voiding unter dem Thermal-Pad die 3D-Röntgenprüfung besteht oder nicht.

Ein Standard-Stencil mit voller Öffnung druckt einen einzigen großen Lotauftrag über das Thermal-Pad. Wenn das Lot während des Reflow schmilzt, wird ausgasender Fluss unter diesem geschmolzenen Pool eingeschlossen. Daraus entstehen Voids, die das darunterliegende POFV-Thermal-Via-Array blockieren.

Das Window-Pane-Stencil unterteilt die Öffnung des Thermal-Pads in ein Raster kleinerer Segmente, getrennt durch pastenfreie Stege, die typischerweise 0,15 bis 0,20 mm breit sind. Während des Reflow entweicht der Flussdampf durch diese Stege, bevor das Lot erstarrt. APTPCB erreicht mit diesem Ansatz konstant weniger als 10 % Thermal-Pad-Voiding, also deutlich unterhalb des Grenzwerts von IPC-A-610H Class 3 mit 30 % und auch unter unserer internen Akzeptanzgrenze von 20 %.

3. Stickstoff-Reflow-Atmosphäre

Immersionssilber oxidiert bei erhöhten Temperaturen. Auch Lotpulver bildet Oberflächenoxide, die die Viskosität erhöhen, das Benetzungsverhalten verschlechtern und Voiding fördern.

Die Reflow-Öfen von APTPCB für 77-GHz-Radarmodule arbeiten in reiner Stickstoffatmosphäre und halten den Rest-Sauerstoffgehalt unter 500 ppm. Stickstoff verhindert das Anlaufen von ImAg, senkt die Oberflächenspannung des Lots für bessere Benetzung auf POFV-Oberflächen und ermöglicht eine Reduzierung der Spitzentemperatur auf 245 bis 250 °C statt 255 bis 260 °C. Dadurch sinkt die kumulative thermische Belastung des PTFE-Dielektrikums.

4. Kontrolliertes Reflow-Profil

| Stufe | Parameter |

|---|---|

| Vorheizrampe | 1,5–2 °C/Sekunde |

| Soak-Zone | 150–180 °C, 60–90 Sekunden |

| Spitzentemperatur | maximal 245–250 °C |

| Zeit über Liquidus | 30–45 Sekunden |

| Abkühlrate | ≤3 °C/Sekunde |

Die kontrollierte Abkühlrate verhindert thermischen Schock an der PTFE/FR-4-Hybridgrenzfläche, also genau dieselbe physikalische Problematik, die auch bei der Bare-Board-Lamination langsame Kühlung erfordert.

3D-Röntgeninspektion: validieren, was optische Inspektion nicht sehen kann

Bottom-terminated RF-Bauteile wie QFN-Transceiver, BGAs oder freiliegende Thermal-Pads haben alle kritischen Lötstellen unter dem Package-Körper verborgen. Standard-AOI-Kameras sehen unterhalb des Gehäuserands nichts.

Die Grenze von 2D-Röntgen: Ein 2D-Bild kollabiert alle Lagen in eine einzige Projektion. Die Kupfersäulen des POFV-Via-Arrays und die darüberliegende Lotschicht erscheinen übereinandergelegt. Eine präzise Void-Messung in der Lotschicht ist so nicht möglich.

3D-AXI mit Computertomographie: Die 3D-Automated-X-Ray-Inspection-Systeme von APTPCB erfassen die Baugruppe aus Dutzenden Winkeln und rekonstruieren ein hochauflösendes 3D-Modell. Qualitätsingenieure schneiden horizontal genau durch die Lotschicht, getrennt von Via-Kupfer darüber und Board-Lagen darunter, und messen Void-Fläche, Verteilung und Position präzise.

APTPCBs Akzeptanzkriterien für Voiding bei RF-Assembly:

| Fehlerart | IPC-A-610H Class 3 | APTPCB intern |

|---|---|---|

| Gesamtes aggregiertes Voiding auf dem Thermal-Pad | ≤30 % | ≤20 % |

| Jeder einzelne isolierte Void | Nicht spezifiziert | ≤5 % der Pad-Fläche |

| Jeder Void über einem POFV-Thermal-Via | Nicht spezifiziert | Nulltoleranz |

Das Nulltoleranzkriterium für Voids über Thermal-Vias ist APTPCB-spezifisch. Ein Void direkt über einem gefüllten Kupfervia trennt den primären Wärmepfad und erzeugt einen lokalen Hotspot, den keine thermische Simulation vorhersagen kann und den kein Design-Margin auffängt.

Feuchtekontrolle vor der Bestückung und Einhaltung von IPC-1601

Die Übergabe in der Lieferkette zwischen Bare-Board-Fertigung und SMT-Bestückung ist der Punkt, an dem viele Zuverlässigkeitsfehler entstehen, Fehler, die sich erst bei thermischen Tests zeigen, deren Ursache aber in mangelhafter Feuchtebehandlung während Transport oder Lagerung liegt.

APTPCBs Handhabungsprotokoll:

- Pre-Bake aller Hybridboards zur Entfernung aufgenommener Feuchte aus den FR-4-Lagen

- Trennung der Boards mit schwefelfreiem Zwischenlagepapier

- Vakuumversiegelung in Moisture Barrier Bags mit kalibrierten Trocknungsmitteln und aktiven HIC-Karten

- Lagerung bei 18–22 °C und <40 % relativer Feuchte bis zum Einsatz an der Linie

Bei Serienfertigungsprogrammen eliminiert die gemeinsame Unterbringung von Bare-Board-Fertigung und SMT-Bestückung unter einem Dach die Transport- und Lagerbelastung vollständig. Die Boards wechseln von der Fertigungslinie direkt auf den SMT-Floor, ohne das klimakontrollierte Gebäude zu verlassen. Das ist die sauberste Umsetzung der Feuchtekontrolle nach IPC-1601.

Das Argument für Turnkey-Fertigung

Die Kombination aus POFV-Thermodesign, Window-Pane-Stencil-Engineering, Stickstoff-Reflow und 3D-AXI-Validierung ist ein zusammenhängendes System. Wenn diese Prozesse auf zwei Lieferanten verteilt werden, also Bare-Board-Fertigung in einem Werk und SMT-Bestückung in einem anderen, zerfällt die Verantwortung für Fehler. Wenn ein Board thermische Tests wegen übermäßigen Voidings nicht besteht, verweist der Bestücker auf POFV-Oberflächenplanarität oder ImAg-Degradation während des Transports. Der Leiterplattenfertiger verweist auf das Reflow-Profil. Die Haftung bleibt beim OEM.

Die vollständige Prozesskette unter einem einzigen Qualitätsmanagementsystem mit gemeinsamen DFM-Datensätzen und Rückverfolgbarkeit nach IATF 16949 zu betreiben, ist der zuverlässigste Weg sicherzustellen, dass das in der Simulation validierte Thermodesign den Kontakt mit der Produktionslinie überlebt. Programme, die vom Prototyp zur Volumenfertigung skalieren, profitieren außerdem davon, dass Prozessdaten aus der Fertigung wie POFV-Planaritätstoleranzen, ImAg-Schichtdickenmessungen und Reflow-Profilaufzeichnungen alle innerhalb eines einheitlichen Serienproduktions-Qualitätssystems verfügbar sind, statt zwischen zwei Lieferanten abgeglichen werden zu müssen. Die vollständige Aufschlüsselung der RO3003-PCB-Kostentreiber, einschließlich der Auswirkungen von Turnkey-Integration auf den Stückpreis gegenüber Split-Vendor-Modellen, liefert den wirtschaftlichen Kontext für diese Entscheidung.

Kontaktieren Sie das Fertigungsteam von APTPCB, wenn Sie ein Turnkey-Angebot für Ihr RO3003-Radarmodul anfordern oder vor Abschluss Ihres Layouts ein thermisches DFM-Review planen möchten.

Referenzen

- Wärmeleitfähigkeit von RO3003 aus Rogers Corporation RO3000® Series Circuit Materials Datasheet (Rev 11.2023).

- Akzeptanz von SMT-Voids gemäß IPC-A-610H Acceptability of Electronic Assemblies, Class 3.

- Feuchtehandhabung gemäß IPC-1601 Printed Board Handling and Storage Guidelines.

- Anforderungen an Via-in-Pad und POFV gemäß IPC-4761 Design Guide for Protection of Printed Board Via Structures.