Contents

- Highlights

- What Is 5G Small Cell PCB? (Scope & Boundaries)

- Metrics That Matter (How to Evaluate It)

- How to Choose (Material & Design Selection)

- Implementation Checkpoints (from Design to Fab)

- Common Mistakes (and How to Avoid Them)

- Supplier Qualification Checklist: How to Vet Your Fab

- Glossary

- 6 Essential Rules for 5G Small Cell PCB (Cheat Sheet)

- FAQ

- Request a Quote / DFM Review for 5G Small Cell PCB

- Conclusion

The deployment of 5G networks has shifted the infrastructure paradigm from massive, sparse towers (Macro Cells) to dense, compact units known as Small Cells. For the PCB engineer and procurement manager, this shift presents a unique paradox: the hardware must be smaller and cheaper to deploy in volume, yet it must handle significantly higher frequencies (mmWave) and thermal loads than ever before. A 5G Small Cell PCB is not merely a scaled-down base station board; it is a high-precision interconnect platform that balances signal integrity, thermal management, and environmental durability.

At APTPCB, we see Small Cell designs pushing the limits of hybrid manufacturing—combining FR4 with high-frequency laminates to achieve cost-effective performance. This guide serves as your definitive engineering handbook, moving beyond basic definitions into the specific material selections, stack-up strategies, and fabrication checkpoints required to launch a successful 5G Small Cell product.

Highlights

- The Hierarchy: Understanding the difference between Femto, Pico, and Micro cell PCB requirements.

- Material Strategy: How to use Hybrid Stackups (FR4 + Rogers/Taconic) to cut costs without killing signal.

- Thermal Management: Solutions for high-power PAs in compact, fanless enclosures.

- Fabrication Criticals: Managing registration and plating in HDI structures.

- Quality Control: Why PIM (Passive Intermodulation) testing is the new standard for acceptance.

- Cost Drivers: Identifying where you are over-specifying and where you cannot afford to cut corners.

What Is 5G Small Cell PCB? (Scope & Boundaries)

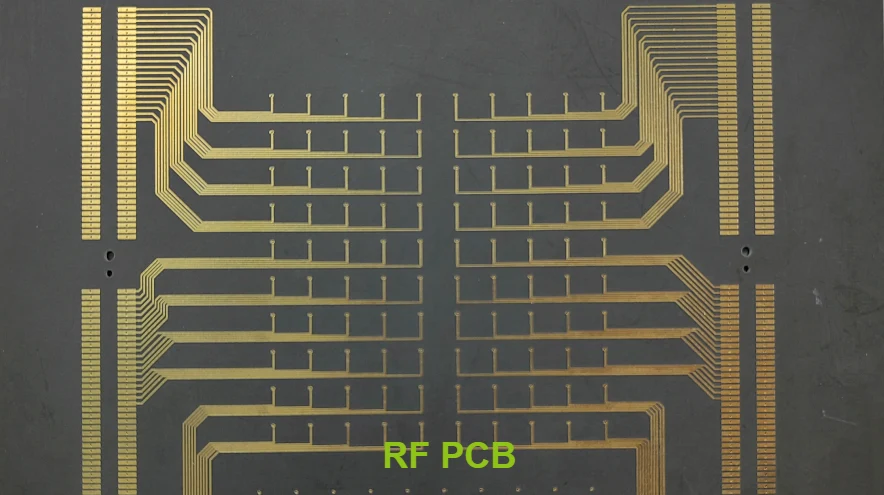

A 5G Small Cell PCB is the core circuit board found in low-power, short-range wireless access points used to densify network coverage. Unlike Macro Cells, which cover miles, Small Cells cover meters (10m to 2km). These PCBs process high-speed data and RF signals, often integrating the antenna array (Active Antenna Unit or AAU) directly onto the board or via a mezzanine connector.

The engineering challenge lies in the frequency. 5G operates in two ranges: Sub-6GHz (similar to 4G but wider bandwidth) and mmWave (24GHz–100GHz). The PCB requirements for mmWave are exponentially more stringent regarding surface roughness, dielectric loss, and layer registration.

The Small Cell Spectrum

- Femtocell: Residential use. Low layer count (4-6 layers), standard HDI, often cost-driven.

- Picocell: Enterprise/Indoor. Moderate complexity (8-12 layers), requires high-speed materials.

- Microcell: Outdoor/Urban. High complexity (12+ layers), ruggedized, high thermal requirements, often utilizes High Frequency PCB materials combined with heavy copper.

Technical Decision Matrix

Every design choice in Small Cell PCBs involves a trade-off between signal integrity (SI) and manufacturability (Yield).

Tech Feature → Buyer Impact

| Technical Feature / Decision | Direct Impact (Yield/Reliability) |

|---|---|

| Hybrid Stackup (FR4 + PTFE) | Reduces material cost by 30-40%, but increases lamination complexity due to different CTE (expansion rates). Risk of delamination if not managed. |

| Embedded Copper Coin | Provides superior heat dissipation for Power Amplifiers (PAs). Increases fabrication cost and lead time; requires precise routing. |

| Surface Finish: ENEPIG | Excellent for wire bonding and soldering; no skin effect signal loss. More expensive than ENIG but critical for high-reliability 5G. |

| Backdrilling (Stubs) | Essential for signal integrity >10Gbps. Reduces signal reflection but requires tight depth tolerance control (+/- 0.05mm). |

Metrics That Matter (How to Evaluate It)

When evaluating a design or a finished board for 5G applications, standard IPC Class 2 checks are insufficient. You must validate RF performance metrics.

| Metric | Target Value (Typical) | Why it Matters for 5G |

|---|---|---|

| Dk (Dielectric Constant) | 3.0 – 3.5 (Stable) | Determines signal propagation speed. Variation causes phase shifts in MIMO antennas. |

| Df (Dissipation Factor) | < 0.002 @ 10GHz | "Loss Tangent." High Df means the signal turns into heat before reaching the antenna. |

| PIM (Passive Intermodulation) | < -160 dBc | Critical for avoiding signal interference. Caused by rough copper or poor solder joints. |

| CTE (z-axis) | < 50 ppm/°C | 5G chips run hot. High expansion breaks plated through-holes (PTH). |

| Copper Roughness | < 0.5 µm (VLP/HVLP) | At mmWave, current travels on the "skin" of the copper. Rough copper acts like a resistor. |

| Thermal Conductivity | > 0.8 W/mK (Dielectric) | Small cells are often fanless; the PCB itself must wick heat away from components. |

How to Choose (Material & Design Selection)

The most common mistake in 5G Small Cell design is using expensive high-frequency material for the entire board. This is rarely necessary.

1. The Hybrid Stackup Strategy

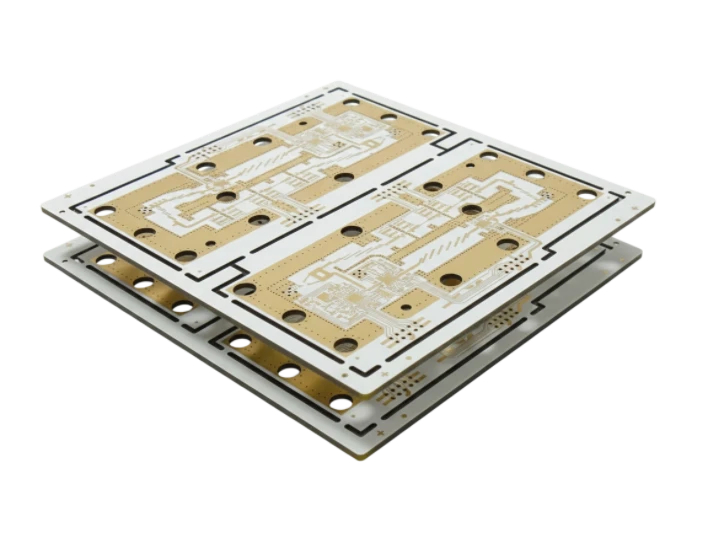

For a 12-layer Small Cell PCB, layers 1-2 and 11-12 (RF layers) should use high-performance materials like Rogers RO4350B, Taconic TLY, or Panasonic Megtron 6/7. The inner layers (digital logic, power distribution) can use standard High-Tg FR4.

- Benefit: Significant cost reduction.

- Challenge: The manufacturer must be expert in managing the lamination cycle, as FR4 and PTFE cure at different rates and pressures.

2. Copper Foil Selection

Standard Electro-Deposited (ED) copper is too rough for 28GHz+ signals. You must specify VLP (Very Low Profile) or HVLP (Hyper Very Low Profile) copper foil. This minimizes the "Skin Effect" loss.

3. Thermal Management Design

Small cells are dense. To manage heat:

- Thermal Vias: Place dense arrays of vias under the PA (Power Amplifier).

- Metal Core: For extreme heat, consider a Metal Core PCB or embedding a copper coin directly under the hot component.

- Solder Mask: Use a thin, low-loss solder mask, or remove the mask entirely over RF transmission lines to prevent signal attenuation.

Implementation Checkpoints (from Design to Fab)

Manufacturing a 5G Small Cell PCB requires a synchronized roadmap. Here are the four critical phases where errors typically occur.

Implementation Roadmap

From Concept to Production

Before CAM, simulate impedance control. Verify that the hybrid material combination (e.g., Rogers + FR4) is balanced to prevent warping. Define blind/buried via structures early.

This is the highest risk phase. Plasma cleaning is mandatory to remove resin smear from PTFE layers before plating. Laser drilling is used for microvias to ensure registration accuracy.

Line width tolerance must be controlled to +/- 10% or better for impedance. Apply Immersion Silver or ENEPIG. Avoid HASL, as the uneven surface ruins RF performance.

Beyond standard E-test, perform TDR (Time Domain Reflectometry) for impedance. For high-end units, conduct PIM testing to ensure no signal distortion exists.

Common Mistakes (and How to Avoid Them)

1. Ignoring the "Glass Weave Effect"

In high-speed 5G signals, if a trace runs parallel to the glass fiber weave of the laminate, it can experience periodic impedance changes (fiber weave skew).

- Fix: Use "Spread Glass" fabric (1067, 1078) or route traces at a 10-degree angle relative to the weave.

2. Poor Cte Management in Hybrid Boards

Mixing materials with vastly different Coefficients of Thermal Expansion (CTE) leads to delamination during reflow soldering.

- Fix: Choose FR4 materials that are specifically formulated to match the Z-axis expansion of the high-frequency laminate. Consult APTPCB’s DFM Guidelines for compatible material pairs.

3. Over-Etching RF Traces

RF traces are often trapezoidal after etching, not perfectly rectangular. This changes the impedance.

- Fix: Account for "Etch Factor" in your simulation software. Ensure your manufacturer uses vacuum etching for finer lines.

Supplier Qualification Checklist: How to Vet Your Fab

Not every PCB house can handle 5G requirements. Use this checklist to vet potential partners.

- Hybrid Lamination Experience: Can they provide cross-section photos of previous hybrid builds (FR4 + PTFE)?

- PIM Testing: Do they have in-house capabilities to test for Passive Intermodulation?

- LDI Capability: Do they use Laser Direct Imaging? (Old film exposure methods are not accurate enough for 5G trace spacing).

- Plasma Etching: Is plasma desmear standard in their process flow for PTFE materials?

- Impedance Tolerance: Can they guarantee +/- 5% impedance tolerance (standard is +/- 10%)?

- Material Stock: Do they stock Rogers/Megtron, or will you face 8-week lead times for materials?

Glossary

PIM (Passive Intermodulation): A type of signal distortion that occurs when two or more signals mix in a non-linear device (like a rusty connector or rough PCB trace), creating interference.

Hybrid Stackup: A PCB design that uses expensive high-frequency materials only on critical signal layers and cheaper FR4 for the rest of the board to save cost.

Skin Effect: The tendency of high-frequency alternating current (AC) to flow near the surface of the conductor. This makes copper surface roughness a critical factor in 5G PCBs.

MIMO (Multiple Input Multiple Output): An antenna technology used in 5G where multiple antennas are used at both the source and the destination. The PCB must support complex antenna arrays.

Backdrilling: The process of drilling out the unused portion of a plated through-hole (stub) to prevent signal reflections in high-speed designs.

6 Essential Rules for 5G Small Cell PCB (Cheat Sheet)

| Golden Rule | Why It Matters | Implementation Key |

|---|---|---|

| 1. Use Hybrid Stackups | Reduces cost by ~40% vs. full PTFE. | Match CTE of FR4 to the HF material. |

| 2. Specify VLP Copper | Reduces insertion loss at mmWave. | Request < 0.5µm roughness profile. |

| 3. Avoid HASL Finish | Uneven pads ruin RF contact/impedance. | Use Immersion Silver or ENEPIG. |

| 4. Backdrill High-Speed Vias | Eliminates signal reflection (stubs). | Keep stub length < 10 mils (0.25mm). |

| 5. Thermal Via Arrays | Small cells have no fans; PCB is the heatsink. | Fill and cap vias under PA components. |

| 6. Early DFM Engagement | Prevents impossible lamination cycles. | Send stackup to fab before routing. |

FAQ

Q: What is the biggest cost driver in 5G Small Cell PCBs?

A: The laminate material. High-frequency materials (like Rogers RO3000/RO4000 series) can be 5x-10x the cost of standard FR4. This is why hybrid stackups are essential for volume production.

Q: Can I use standard FR4 for 5G applications?

A: For Sub-6GHz applications, high-performance FR4 (like Isola I-Speed) might suffice for short traces. However, for mmWave (24GHz+), standard FR4 has too much dielectric loss (Df) and moisture absorption, making it unusable for signal layers.

Q: Why is ENEPIG the recommended surface finish?

A: ENEPIG (Electroless Nickel Electroless Palladium Immersion Gold) offers the best balance. It provides a flat surface for fine-pitch components, excellent wire-bonding capability, and unlike ENIG, it doesn't suffer from "Black Pad" issues. It is highly reliable for outdoor environments.

Q: How do I manage heat in a sealed Small Cell unit?

A: Since fans are rarely used, the PCB must conduct heat to the enclosure. Use heavy copper (2oz+), embedded copper coins, or Metal Core PCBs for the power amplifier section. Thermal interface materials (TIM) connect the PCB hot spots to the chassis.

Q: What is the lead time for 5G Small Cell PCB prototypes?

A: Standard lead time is 10-15 days. However, if specialized materials (uncommon Rogers/Taconic variants) are not in stock, lead times can extend to 4-6 weeks. Always check material availability with APTPCB during the design phase.

Q: Do I need blind and buried vias?

A: Almost certainly. To achieve the density required for Small Cells (especially with MIMO antenna arrays), HDI PCB technology using blind and buried vias is necessary to route signals without increasing the board size.

Request a Quote / DFM Review for 5G Small Cell PCB

Ready to move your 5G design from simulation to reality? At APTPCB, we specialize in high-frequency, hybrid, and HDI fabrication.

To get an accurate quote and DFM analysis, please provide:

- Gerber Files: RS-274X or ODB++ format.

- Stackup Diagram: Clearly indicating material types (e.g., Layer 1: Rogers 4350B, Layer 2: FR4).

- Impedance Requirements: Specific trace widths and target ohms.

- Drill Chart: Defining blind/buried via pairs.

- Quantity: Prototype vs. Mass Production estimates.

Conclusion

5G Small Cell PCBs represent the intersection of advanced material science and precision manufacturing. They require a departure from traditional "FR4 thinking." By understanding the nuances of hybrid stackups, strict PIM control, and thermal management, you can deploy reliable network infrastructure that withstands the demands of the 5G era.

Whether you are building a Femtocell for a home office or a ruggedized Microcell for a city streetlamp, the success of your product relies on the integrity of the PCB. Ensure you partner with a manufacturer who understands the physics of high-frequency signals.

Explore more about our capabilities: