| Megtron 4 (R-5725 / R-5620) | Modified PPE resin / E-glass | 3.8 | 0.005 | Low-loss FR-4 alternative. Tg 176 deg C, Td 360 deg C. Processes with standard FR-4 equipment and chemistry. Lead-free and RoHS compliant. Good balance of electrical performance and cost for mid-speed digital applications. | PCIe Gen3/Gen4, 10–25 Gbps SerDes, network routers, server boards, measuring instruments |

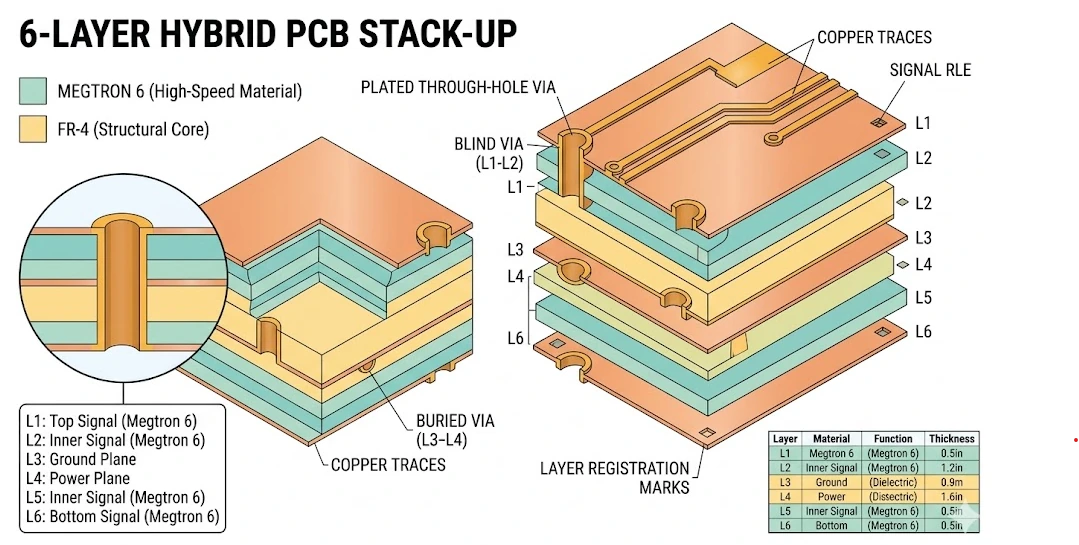

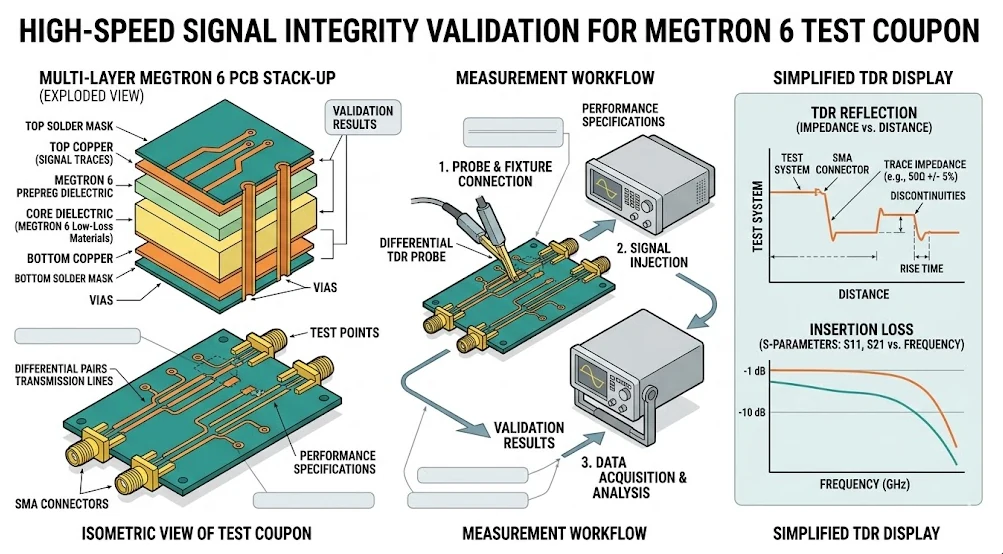

| Megtron 6 (R-5775 / R-5670) | PPE resin / E-glass (standard and low-Dk glass) | 3.4 (N-glass) / 3.7 (E-glass) | 0.002 | Ultra-low-loss, industry benchmark for high-speed digital. Tg 185 deg C, Td 410 deg C. Available with standard E-glass or low-Dk N-glass. Excellent HDI and thermal performance. FR-4-compatible processing. Spread-glass weave options for skew control. | 56G PAM4 backplanes, data center switches, 400G Ethernet, AI/HPC interconnects, high-speed IC testers |

| Megtron 7 (R-5785 / R-5680) | Advanced PPE resin / E-glass (standard and low-Dk glass) | 3.3 (N-glass) / 3.6 (E-glass) | 0.0015 | Next-generation ultra-low-loss with improved Z-axis CTE for high-layer-count reliability. Tg 200 deg C, Td 400 deg C. 30-40% longer viable channel length vs. Megtron 6. Robust IST microvia reliability for high-layer-count backplanes. | 112G PAM4 backplanes, 800G Ethernet switches, HPC/AI server interconnects, next-gen switch ASIC host boards |

| Megtron 8 (R-5795 / R-5690) | Next-gen ultra-low-loss resin / E-glass | 3.1 | 0.0012 | Panasonic's latest ultra-low-loss grade for the most demanding next-generation channels. Tg 220 deg C, Td 370 deg C. Designed for 224G PAM4 and beyond. FR-4-compatible processing maintained. | 224G PAM4, next-gen co-packaged optics, 1.6T Ethernet, advanced AI accelerator interconnects |

| R-1755V | High-Tg FR-4 epoxy / E-glass | 4.4 | 0.016 | Standard high-Tg FR-4 baseline from Panasonic. Tg 173 deg C, Td 350 deg C. Cost-effective option for non-critical signal layers in hybrid stack-ups or applications where electrical loss is not the primary concern. | Power/ground layers in hybrid stacks, general multilayer PCBs, non-critical digital, cost-sensitive applications |