Compute

Compute accelerator

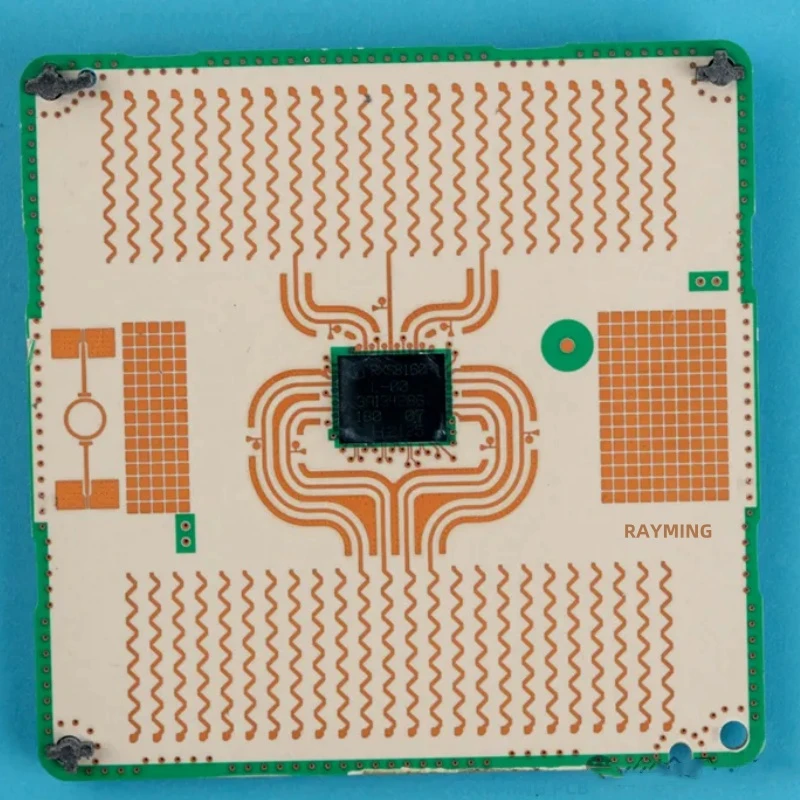

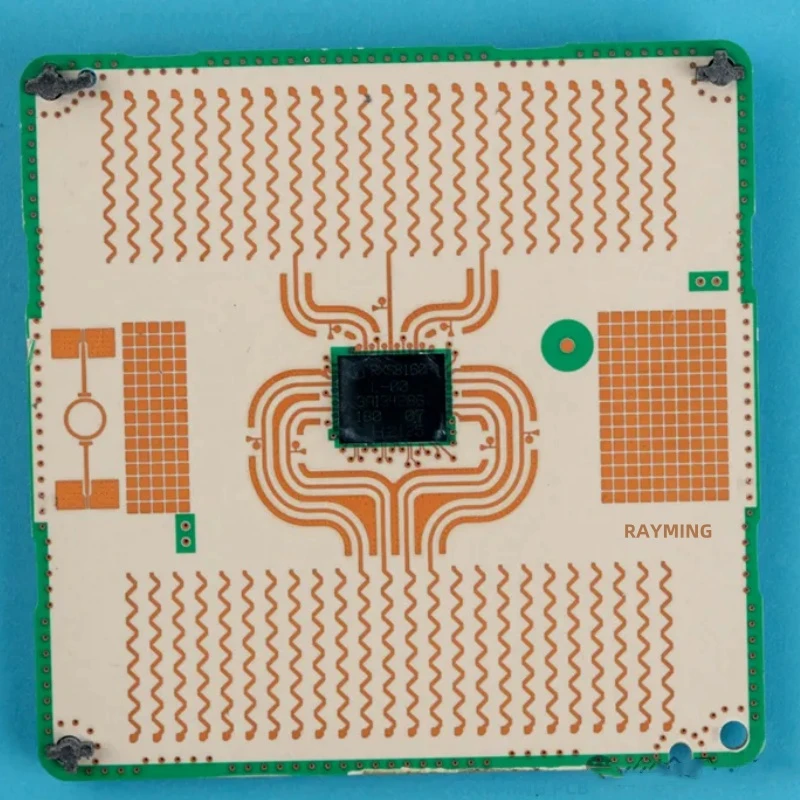

0.3 mm BGA with boundary-scan, underfill, and vacuum reflow logs.

Boundary-scanUnderfillVacuum

0.3 MM PITCH • 01005 • VOID CONTROL

DFM, stencil/paste, ±25 µm placement, nitrogen reflow, AXI/void tracking, underfill, and controlled rework keep hidden joints reliable across pilots and volume lots.

We pair process controls with inspection data so hidden joints ship with evidence.

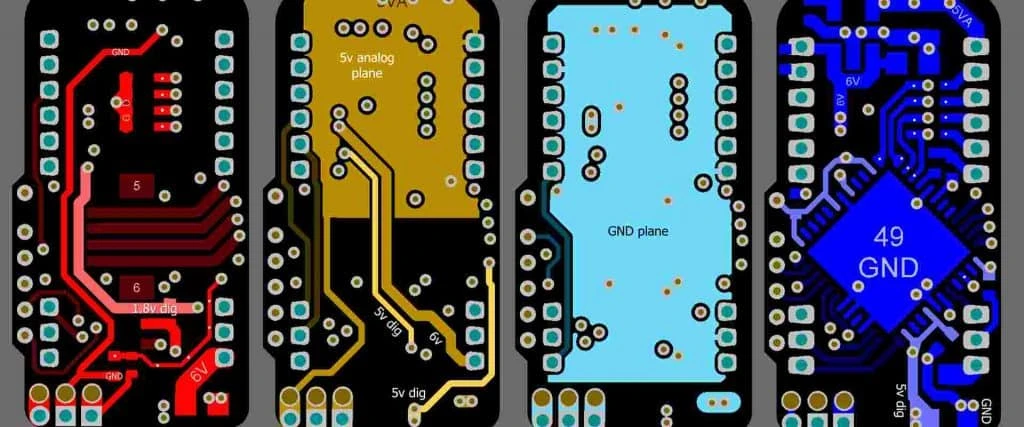

Via-in-pad, PoP, copper-filled microvias supported.

Vision + vacuum support keep CpK ≥1.33.

Stencil/paste/profile tuning + vacuum dwell.

COVERAGE

Every gate—DFM, stencil, placement, reflow, inspection, underfill, rework—is coordinated by the same team so yield holds and rework cycles stay controlled.

DFM & land pattern

Pad design, mask clearance, via-in-pad fills, and copper balance reviews limit warpage.

Stencil & paste

80–120 µm step/nano stencils, Type 5/6 paste, and support tooling lock print windows.

Placement & reflow

±25 µm placement, vacuum support, nitrogen reflow ΔT ≤5 °C with thermocouples.

Inspection & rework

3D AOI, sample AXI, void reports, underfill, staking, and ≤3-cycle rework procedures.

PLAYBOOK

Defined gates keep high-density BGA/QFN builds stable from intake through rework.

Package intake

Collect drawings, pad stacks, paste specs, and void targets.

Process tuning

Stencil/paste selection, placement, and reflow simulations.

Production run

SMT with 100% SPI/AOI, vacuum support, and nitrogen reflow.

Inspection & analytics

AXI, void reports, ionic checks, and SPC dashboards.

Underfill & rework

Execute underfill/staking and controlled ≤3-cycle rework with post-AXI.

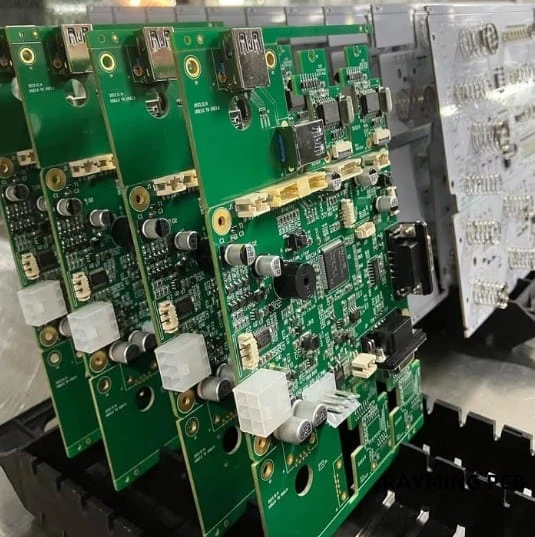

PORTFOLIO

Hidden-joint builds we run every quarter with documented void control and rework limits.

CAPABILITIES

Tools, fixtures, and analytics sized for hidden-joint success.

Dedicated reflow, AXI, underfill, and rework labs with humidity control.

QUALITY

Inline inspection, AXI, and void analytics make hidden joints visible.

Area-ratio checks, paste height SPC, and printer feedback loops.

AXI sampling and C-SAM/void reports with <10% BTC targets.

≤3 cycles with site dressing, paste print, and post-AXI verification.

High-density BGAs with boundary-scan, underfill, and rework traceability.

Cleanliness, AOI/AXI, and rework logs for Class II/III devices.

Void/hi-pot data and PPAP-ready evidence for ECUs and inverters.

Shielded RF modules with controlled reflow and void targets.

Everything you need to know about HDI PCB technology

Upload your files to receive a DFM, process, and inspection plan for hidden joints.