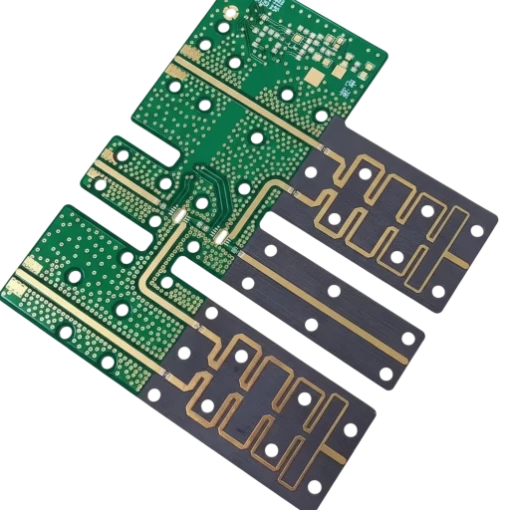

Electronic warfare and secure communications demand hardware that withstands intentional interference. An Anti-Jamming PCB is not just a standard circuit board; it is a precision-engineered component designed to suppress electromagnetic interference (EMI), maintain signal integrity under duress, and support advanced filtering algorithms. Engineers designing for defense, aerospace, or high-security industrial sectors must adhere to strict layout and material protocols to ensure resilience. APTPCB (APTPCB PCB Factory) specializes in fabricating these high-reliability boards, ensuring that theoretical anti-jamming capabilities translate into physical performance.

Anti-Jamming PCB quick answer (30 seconds)

Designing a robust Anti-Jamming PCB requires focusing on signal isolation and material stability.

- Material Selection: Use low-loss laminates (Rogers, Taconic, or Isola) with a stable Dielectric Constant (Dk) across wide frequency ranges to prevent signal phase shifts.

- Grounding Strategy: Implement a continuous ground reference plane for every signal layer. Use "via stitching" along board edges and critical traces to create Faraday cages.

- Impedance Control: Maintain strict impedance tolerances (typically ±5% or ±7%) to minimize signal reflections that jammers can exploit.

- Isolation: Physically separate analog (RF) sections from digital logic to prevent internal noise from lowering the jamming threshold.

- Shielding: Integrate footprints for board-level shielding cans or utilize embedded capacitance materials to dampen high-frequency noise.

- Validation: Verify performance using Time Domain Reflectometry (TDR) and Vector Network Analyzer (VNA) testing during the prototype phase.

When Anti-Jamming PCB applies (and when it doesn’t)

Understanding the operational environment is critical before committing to the higher costs of a Jamming Resistant PCB.

When to use Anti-Jamming PCB:

- AESA Radar Systems: Active Electronically Scanned Array radars require precise phase control and isolation between thousands of transmit/receive modules.

- GNSS/GPS Receivers: Military and critical infrastructure navigation systems that must reject spoofing and jamming signals.

- Secure Tactical Radios: Communication devices operating in contested electromagnetic environments.

- High-Voltage Substations: Control boards that must operate reliably near massive switching noise sources.

- Autonomous Drone Defense: UAVs requiring uncompromised control links in hostile territories.

When standard PCBs are sufficient:

- Consumer Electronics: Household appliances and toys do not face intentional jamming threats.

- Low-Speed Digital Logic: Simple microcontrollers operating under 50 MHz typically do not require exotic anti-jamming materials.

- Indoor IoT Sensors: Devices in controlled Wi-Fi environments usually suffice with standard FR4 and basic EMI practices.

- General Industrial Controls: Unless placed directly next to high-power VFDs or arc welders, standard industrial IPC Class 2 boards are adequate.

Anti-Jamming PCB rules and specifications (key parameters and limits)

To achieve high interference rejection, the manufacturing process must adhere to tight tolerances. The following table outlines critical specifications for an effective Anti-Jamming PCB.

| Rule | Recommended Value/Range | Why it matters | How to verify | If ignored |

|---|---|---|---|---|

| Dielectric Constant (Dk) | 3.0 – 3.5 (Stable ±0.05) | Determines signal propagation speed; variation causes phase errors. | Material datasheet & TDR test. | Phase mismatch degrades beamforming accuracy. |

| Dissipation Factor (Df) | < 0.002 @ 10 GHz | Minimizes signal attenuation, preserving weak signals against noise. | VNA insertion loss measurement. | Signal loss reduces effective range and sensitivity. |

| Trace Width Tolerance | ±0.5 mil (±12 µm) | Directly impacts impedance control. | Cross-section analysis (microsection). | Impedance mismatch causes reflections (VSWR). |

| Via Stitching Pitch | < λ/20 of highest freq | Creates an effective Faraday cage to block lateral EMI. | Visual inspection & Gerber review. | RF leakage allows jamming signals to penetrate. |

| Copper Roughness | VLP or HVLP (< 2 µm) | Reduces skin effect losses at high frequencies. | SEM (Scanning Electron Microscope). | Increased insertion loss at mmWave frequencies. |

| Layer Registration | ±3 mil (±75 µm) | Ensures vertical alignment of coupled structures and grounds. | X-Ray inspection. | Misalignment ruins broadside coupling and impedance. |

| Ground Plane Continuity | 100% solid (no splits) | Provides low-inductance return path. | AOI (Automated Optical Inspection). | Ground loops and high EMI susceptibility. |

| Plated Through Hole (PTH) Wall | > 25 µm copper | Ensures robust grounding and thermal reliability. | Microsection analysis. | Via cracking under thermal stress; intermittent grounding. |

| Solder Mask Web | > 3 mil (0.075 mm) | Prevents solder bridging between fine-pitch pads. | Visual / AOI. | Short circuits on high-density RF components. |

| Surface Finish | ENIG or Immersion Silver | Provides flat surface for fine-pitch components and skin-effect conductivity. | X-Ray Fluorescence (XRF). | Signal loss or poor solder joints on BGA/QFN. |

Anti-Jamming PCB implementation steps (process checkpoints)

Building an Anti-Jamming PCB involves specific actions at every stage of the design and manufacturing workflow.

- Define Frequency & Threat Profile:

- Action: Identify the operating frequency range (e.g., L-band, X-band) and expected jamming power levels.

- Check: Confirm if the design requires High Frequency PCB materials or hybrid stackups.

- Select Substrate Material:

- Action: Choose materials like Rogers RO4350B or RO3003 for RF layers, potentially bonding with FR4 for digital layers to save cost.

- Check: Verify CTE (Coefficient of Thermal Expansion) compatibility between hybrid materials.

- Design the Stackup:

- Action: Configure a symmetrical stackup with ground planes immediately adjacent to high-speed signal layers.

- Check: Use a PCB Stack-up calculator to confirm impedance targets.

- Layout Critical Traces (3W Rule):

- Action: Route RF traces with a spacing of at least 3 times the trace width (3W) to minimize crosstalk.

- Check: Run DRC (Design Rule Check) specifically for trace-to-trace clearance.

- Implement Via Stitching:

- Action: Place ground vias along the perimeter of the board and around sensitive RF blocks (guard rings).

- Check: Ensure via pitch is tight enough to block the target wavelength.

- Optimize Return Paths:

- Action: Ensure no traces cross splits in the reference ground plane.

- Check: Visual review of layer 2 and layer 3 (or adjacent reference layers).

- Add Shielding Footprints:

- Action: Design landing pads for metal shielding cans over sensitive oscillators and front-end modules.

- Check: Verify mechanical clearance for the shield in 3D view.

- Fabrication Data Generation:

- Action: Export ODB++ or Gerber X2 files containing impedance tables and material specs.

- Check: Include a "Read Me" file specifying "Anti-Jamming requirements" and IPC Class 3 if needed.

Anti-Jamming PCB troubleshooting (failure modes and fixes)

Even with robust designs, issues can arise. Here is how to diagnose common failures in Anti-Jamming PCB deployments.

- Symptom: High Bit Error Rate (BER) under load.

- Cause: Power Supply Rejection Ratio (PSRR) is too low; noise from power rails is coupling into RF lines.

- Check: Probe power rails for ripple; check decoupling capacitor placement.

- Fix: Add ferrite beads and low-ESR capacitors close to active pins; increase power plane capacitance.

- Symptom: Signal drift or loss of lock.

- Cause: Thermal instability of the dielectric material (high Tcdk).

- Check: Verify operating temperature vs. material specs.

- Fix: Switch to a thermally stable material like Rogers RO4000 series; improve thermal management (heatsinks).

- Symptom: Unexpected spurious emissions.

- Cause: Resonant cavities formed between ground planes due to insufficient via stitching.

- Check: Near-field probe scan to locate hot spots.

- Fix: Add "randomized" stitching vias to break up resonant modes.

- Symptom: Poor isolation between channels (Crosstalk).

- Cause: Parallel trace runs are too long or too close.

- Check: Review layout for violations of the 3W rule.

- Fix: Separate traces with a ground guard trace; use differential signaling where possible.

- Symptom: Impedance mismatch (High VSWR).

- Cause: Over-etching during manufacturing reducing trace width.

- Check: TDR measurement and cross-section analysis.

- Fix: Adjust trace width compensation in CAM files; tighten etching tolerance at the factory.

- Symptom: Delamination under thermal stress.

- Cause: Mismatched CTE in hybrid stackups (e.g., PTFE vs. FR4).

- Check: Thermal shock test results.

- Fix: Use high-Tg prepregs compatible with the RF core; adjust lamination cycle parameters.

How to choose Anti-Jamming PCB (design decisions and trade-offs)

Selecting the right configuration for an Anti-Jamming PCB involves balancing performance against cost and manufacturability.

1. Hybrid vs. Pure RF Stackup

- Hybrid: Uses expensive RF material only on the top/bottom layers and standard FR4 for the core.

- Pros: Lower cost, sufficient for many L-band/S-band applications.

- Cons: Complex lamination process; potential warping issues.

- Pure RF: Uses uniform high-frequency material throughout.

- Pros: Best electrical performance, consistent CTE.

- Cons: Significantly higher material cost.

2. Surface Finish Selection

- ENIG (Electroless Nickel Immersion Gold): Good shelf life and flat surface. However, nickel is magnetic and can cause passive intermodulation (PIM) in sensitive RF circuits.

- Immersion Silver: Excellent conductivity and non-magnetic. Best for high-frequency anti-jamming but tarnishes easily if not handled correctly.

- OSP: Lowest cost, good for RF, but short shelf life.

3. Shielding: Cans vs. Embedded

- Metal Cans: Traditional, effective, and reworkable. Adds weight and height.

- Embedded/Cavity Shielding: Milling cavities into the PCB to house components, then plating over. Reduces profile but increases manufacturing cost and complexity.

4. Via Technology

- Through-Hole Vias: Cheapest but create stubs that act as antennas at high frequencies.

- Back-drilled Vias: Removes the unused stub portion. Essential for signals > 5 Gbps or > 3 GHz to maintain signal integrity.

Anti-Jamming PCB FAQ (cost, lead time, common defects, acceptance criteria, Design for Manufacturability (DFM) files)

Q: How much does an Anti-Jamming PCB cost compared to a standard PCB? A: Expect costs to be 3x to 10x higher than standard FR4 boards. The price driver is the specialized laminate (e.g., Rogers PCB Materials), tighter tolerance requirements (impedance control), and often the need for hybrid lamination cycles.

Q: What is the typical lead time for manufacturing these boards? A: Standard lead time is 10–15 working days. If specialized materials (like specific Rogers or Taconic cores) are not in stock, lead time can extend to 3–4 weeks. APTPCB stocks common high-frequency materials to expedite this process.

Q: What are the acceptance criteria for Anti-Jamming PCBs? A: Acceptance is usually based on IPC-6012 Class 3 standards. Key criteria include TDR impedance verification (pass/fail based on tolerance), clean cross-sections showing no delamination, and passing ionic contamination tests to prevent leakage currents.

Q: Can I use standard FR4 for an Anti-Jamming design? A: Generally, no. FR4 has a high Dissipation Factor (Df) and unstable Dielectric Constant (Dk) at high frequencies, which degrades signal integrity. However, FR4 can be used in hybrid stackups for non-critical digital layers.

Q: What files are required for a DFM review of an Anti-Jamming PCB? A: You must provide Gerber files (or ODB++), a detailed stackup drawing specifying material types and layer order, an IPC netlist for electrical test verification, and a drill drawing identifying back-drill locations if applicable.

Q: How does an AESA Radar PCB differ from a standard Anti-Jamming PCB? A: An AESA Radar PCB is a subset of anti-jamming boards that requires extreme phase matching between channels. It often involves hundreds of layers of complex beamforming networks and demands the tightest possible etching tolerances to ensure all antenna elements radiate in perfect phase.

Q: What is the most common defect in Jamming Resistant PCBs? A: The most common defect is "impedance discontinuity." This occurs when trace widths vary during etching or when reference planes are interrupted, causing signal reflections that reduce the system's ability to filter out jamming noise.

Q: Does APTPCB offer testing for anti-jamming performance? A: We perform board-level electrical testing (Open/Short) and impedance testing (TDR). Functional anti-jamming testing (simulating interference) is typically performed by the customer at the system assembly level, as it requires proprietary software and hardware.

Q: How do buried capacitors help in Anti-Jamming designs? A: Buried capacitance layers (using very thin dielectrics between power and ground) provide excellent high-frequency decoupling. This lowers the power distribution network (PDN) impedance, reducing noise that could otherwise desensitize the receiver.

Q: What is the impact of surface roughness on these PCBs? A: At frequencies above 10 GHz, current flows primarily along the "skin" of the conductor. Rough copper increases the path length, leading to higher insertion loss. We recommend VLP (Very Low Profile) copper for all high-frequency anti-jamming designs.

Resources for Anti-Jamming PCB (related pages and tools)

To further optimize your design, consult these specific resources:

- Industry Application: Aerospace & Defense PCB – Standards and requirements for military-grade boards.

- Material Data: Rogers PCB Materials – Specs for the most common anti-jamming substrates.

- Design Guide: High Frequency PCB – General rules for RF and microwave circuits.

- Stackup Planning: PCB Stack-up – How to arrange layers for optimal signal integrity.

Anti-Jamming PCB glossary (key terms)

| Term | Definition | Relevance to Anti-Jamming |

|---|---|---|

| EMI (Electromagnetic Interference) | Disturbance generated by an external source that affects an electrical circuit. | The primary threat an anti-jamming PCB is designed to resist. |

| Impedance Control | Maintaining a specific resistance to AC signals (e.g., 50Ω) along a trace. | Prevents signal reflections that jammers can exploit to degrade performance. |

| Faraday Cage | An enclosure formed by conductive material (or vias) to block electromagnetic fields. | Used on PCBs via stitching vias to isolate sensitive RF sections. |

| Dk (Dielectric Constant) | A measure of a material's ability to store electrical energy in an electric field. | Stability of Dk is crucial for maintaining phase accuracy in radar systems. |

| Df (Dissipation Factor) | A measure of the power loss rate in a dielectric material. | Low Df materials are required to preserve weak signals in jamming environments. |

| Crosstalk | Unwanted signal transfer between communication channels. | Must be minimized to prevent internal noise from lowering the jamming threshold. |

| Back-drilling | Removing the unused portion of a plated through-hole (stub). | Eliminates signal reflections in high-speed/high-frequency links. |

| Hybrid Stackup | A PCB stackup using different materials (e.g., Rogers + FR4). | Balances cost and performance for complex anti-jamming systems. |

| Skin Effect | The tendency of high-frequency current to flow near the surface of a conductor. | Requires smooth copper profiles to minimize losses. |

| TDR (Time Domain Reflectometry) | A measurement technique used to determine the impedance of PCB traces. | The standard method for verifying manufacturing quality of RF boards. |

Request a quote for Anti-Jamming PCB (Design for Manufacturability (DFM) review + pricing)

Ready to move from design to prototype? APTPCB provides comprehensive DFM reviews to ensure your Anti-Jamming PCB meets all impedance and material specifications before production begins.

For the most accurate quote, please provide:

- Gerber Files: RS-274X or ODB++ format.

- Fabrication Drawing: Include stackup details, material requirements (e.g., Rogers 4350B), and impedance tables.

- Quantity & Lead Time: Prototype or mass production volume.

- Special Requirements: Back-drilling, Class 3 inspection, or specific surface finishes.

Conclusion (next steps)

Successfully deploying an Anti-Jamming PCB requires a synergy between advanced design techniques and precision manufacturing. By strictly controlling material properties, impedance, and shielding, engineers can build systems that maintain integrity in the most hostile electromagnetic environments. Whether for AESA radar or secure communications, the choice of manufacturer is as critical as the design itself. Ensure your partner has the capability to handle hybrid stackups and tight-tolerance RF requirements to guarantee mission success.