Definition, scope, and who this guide is for

Automotive Ethernet has rapidly become the backbone of modern vehicle architectures, replacing legacy protocols like CAN and LIN for high-bandwidth applications such as ADAS, infotainment, and autonomous driving systems. Unlike standard office Ethernet, Automotive Ethernet PCB layout focuses on single-pair Ethernet (SPE) standards like 100BASE-T1 and 1000BASE-T1, which transmit data over unshielded twisted pairs (UTP) to reduce weight and cabling costs. This shift places an immense burden on the printed circuit board (PCB) design to maintain signal integrity in a noisy, harsh automotive environment.

This guide is written for engineering leads, PCB designers, and procurement managers who need to transition from concept to mass production without compromising reliability. It moves beyond basic theory to provide actionable specifications, risk mitigation strategies, and validation protocols. Whether you are designing a zonal controller or a high-speed camera module, the layout decisions you make today will determine the electromagnetic compatibility (EMC) and functional safety of the final product.

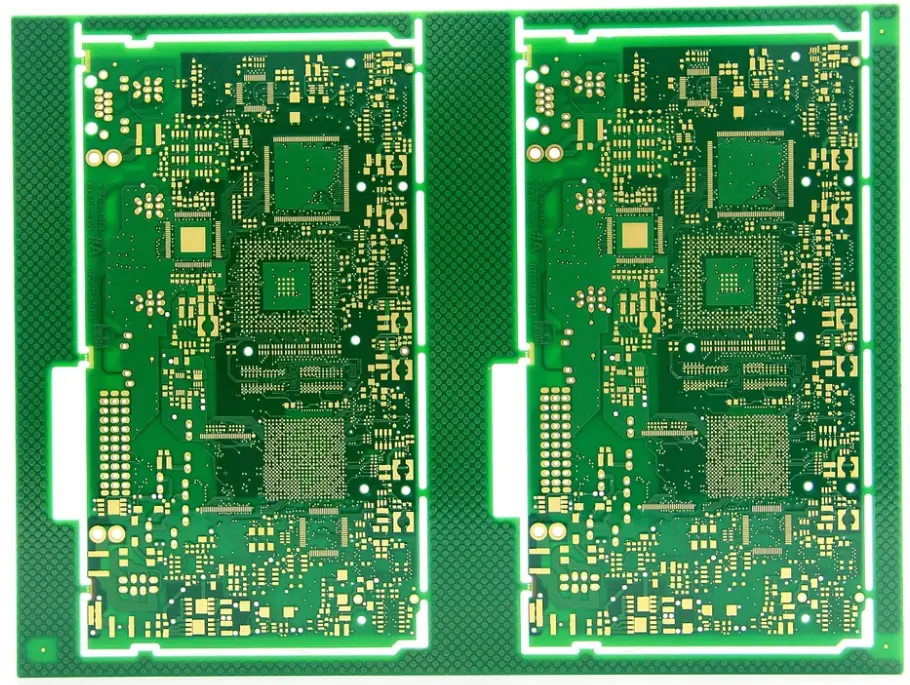

At APTPCB (APTPCB PCB Factory), we see many designs fail not because of the chipset, but because the physical layout did not account for the strict impedance and noise immunity requirements of automotive standards. This playbook serves as your roadmap to navigating those challenges, ensuring your documentation is robust enough for manufacturing and your suppliers are qualified to execute your vision.

When to use Automotive Ethernet PCB layout (and when a standard approach is better)

Understanding the scope defined above helps clarify exactly when to deploy specialized layout techniques versus standard routing methods.

While traditional protocols like CAN, LIN, or FlexRay are sufficient for low-speed control signals (windows, seats, basic sensors), they cannot handle the gigabit data rates required by LIDAR, 4K cameras, or domain controllers. Automotive Ethernet PCB layout is mandatory when your system requires bandwidth exceeding 10 Mbps while demanding lighter cabling than shielded LVDS or coaxial solutions. It is the specific choice for full-duplex communication over a single pair of wires where weight reduction is a priority.

However, a standard PCB layout approach is better if your application is purely low-speed or if you are using standard RJ45 Ethernet for diagnostic ports (OBD) that do not face the same weight constraints or continuous vibration issues as internal vehicle networks. If the interface is merely for end-of-line programming in a controlled factory environment, the rigorous constraints of 1000BASE-T1 layout—such as strict mode conversion limits and specialized material selection—might be over-engineering.

Use specialized Automotive Ethernet layout rules when:

- Bandwidth is critical: You are moving 100 Mbps to 10 Gbps of data.

- Weight is a constraint: You are using unshielded twisted pair (UTP) cabling.

- EMI is a concern: The system operates near high-power inverters or motors.

- Reliability is non-negotiable: The link supports safety-critical ADAS functions.

Automotive Ethernet PCB layout specifications (materials, stackup, tolerances)

Once you have determined that your design requires high-speed automotive protocols, the next step is defining the rigid specifications that will govern the manufacturing process.

To ensure signal integrity and manufacturability, you must define the following parameters explicitly in your fabrication notes. Vague requests like "impedance control required" are insufficient for Automotive Ethernet PCB layout.

- Differential Impedance:

- Target: 100 Ohms ± 10% (or ± 5% for 10Gbps+ applications).

- Context: This matches the characteristic impedance of the UTP cabling to minimize reflections.

- Dielectric Materials (Dk/Df):

- Requirement: Use materials with stable Dielectric Constant (Dk) and low Dissipation Factor (Df) over wide frequency ranges.

- Range: Df < 0.010 at 1 GHz for 1000BASE-T1; Df < 0.005 for Multi-Gig.

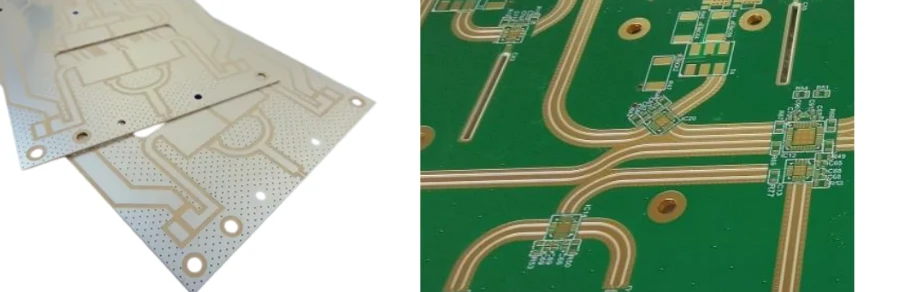

- Examples: High-Tg FR4 (Isola 370HR) for lower speeds; Megtron 6 or Rogers RO4000 series for high-speed zones.

- PCB Stackup Symmetry:

- Requirement: Fully symmetrical stackup to prevent warpage during reflow and maintain consistent impedance.

- Detail: Signal layers should be adjacent to solid ground reference planes.

- Copper Roughness:

- Specification: Very Low Profile (VLP) or HVLP copper foil.

- Reason: Reduces skin effect losses at high frequencies (>1 GHz).

- Trace Width and Spacing:

- Target: Calculated based on stackup to achieve 100 Ohms.

- Tolerance: Etch tolerance must be controlled to ± 0.5 mil or ± 10%, whichever is tighter.

- Intra-Pair Skew:

- Limit: < 5 mils (0.127 mm) mismatch within the differential pair.

- Impact: High skew converts differential mode signals to common mode noise, failing EMC tests.

- Insertion Loss:

- Budget: Define maximum loss per inch (e.g., -0.5 dB/inch at Nyquist frequency).

- Validation: Must be verified via simulation or test coupons.

- Return Loss:

- Limit: Typically < -20 dB up to the Nyquist frequency.

- Significance: Measures how much signal is reflected back to the source.

- Glass Weave Style:

- Specification: Spread glass (e.g., 1067, 1078) or mechanically rotated routing (10-15 degrees).

- Prevention: Mitigates the Fiber Weave Effect (FWE) which causes periodic impedance variations.

- Via Design:

- Requirement: Minimized via stubs.

- Action: Use backdrilling or blind/buried vias for signals > 1 Gbps to remove resonant stubs.

- Solder Mask:

- Detail: Account for solder mask Dk in impedance calculations (usually lowers impedance by 2-3 Ohms).

- Color: Typically Green or Black, but ensure thickness consistency.

- Environmental Reliability:

- Standard: AEC-Q100 equivalent for board stress; Thermal cycling -40°C to +125°C (or +150°C for engine compartments).

Automotive Ethernet PCB layout manufacturing risks (root causes and prevention)

Even with perfect specifications, the transition from digital design to physical board involves risks that can compromise the Automotive Ethernet PCB layout.

Understanding these failure modes allows you to implement detection methods early in the NPI (New Product Introduction) phase.

- Impedance Discontinuity at Connectors

- Root Cause: The footprint of the MDI (Medium Dependent Interface) connector often breaks the reference plane or requires pad sizes that deviate from the 100-ohm geometry.

- Detection: TDR (Time Domain Reflectometry) simulation shows a spike at the connector interface.

- Prevention: Use ground cutouts carefully under pads to increase inductance or add ground vias to reduce it; simulate the connector breakout area.

- Reference Plane Gaps (Return Path Breaks)

- Root Cause: Routing differential pairs over split power planes or voids in the ground plane.

- Detection: Visual inspection of inner layers; EMI near-field scanning.

- Prevention: Ensure continuous solid ground reference along the entire path of the differential pair. Stitching vias must be used if changing layers.

- Mode Conversion (Differential to Common Mode)

- Root Cause: Asymmetry in the physical layout (e.g., one trace is longer, or one trace is closer to a piece of metal/ground pour than the other).

- Detection: Mixed-mode S-parameter measurements (SDC11/SDC21).

- Prevention: Maintain strict symmetry; avoid routing near board edges or tall components; remove "poured" ground between the differential pair legs.

- Crosstalk from Aggressor Signals

- Root Cause: High-voltage switching lines (e.g., from DC-DC converters) routed too close to the Ethernet pairs.

- Detection: Near-end Crosstalk (NEXT) and Far-end Crosstalk (FEXT) testing.

- Prevention: Maintain "3W" or "5W" spacing rules (3x or 5x trace width) between Ethernet pairs and other signals. Use guard traces or ground via fences if space permits.

- Fiber Weave Effect (FWE)

- Root Cause: One leg of the differential pair runs on top of a glass bundle while the other runs over resin, causing different propagation speeds.

- Detection: Phase mismatch seen in high-frequency measurements; difficult to detect with standard TDR.

- Prevention: Use "spread glass" dielectrics or route traces at a slight angle (10°) relative to the weave.

- Via Stub Resonance

- Root Cause: Unused portions of plated through-hole vias act as antennas at specific frequencies (quarter-wave resonance).

- Detection: Sharp dip in Insertion Loss plot at high frequencies.

- Prevention: Specify backdrilling for through-holes or use blind/buried vias for critical high-speed nets.

- Copper Etch Variation

- Root Cause: Manufacturing process variation leads to trapezoidal trace shapes rather than rectangular, altering impedance.

- Detection: Cross-section analysis (microsection) of coupons.

- Prevention: Include etch factor in impedance modeling; choose a supplier with automated optical inspection (AOI) for fine lines.

- CAF (Conductive Anodic Filament) Growth

- Root Cause: Electrochemical migration along the glass fibers between biased vias in harsh automotive environments.

- Detection: High-voltage insulation resistance testing; long-term reliability stress tests.

- Prevention: Use CAF-resistant materials; increase spacing between vias connected to different potentials.

- Thermal Expansion Mismatch

- Root Cause: Different CTE (Coefficient of Thermal Expansion) between the PCB substrate and large automotive connectors or BGAs.

- Detection: Solder joint cracking after thermal cycling.

- Prevention: Match CTE of the PCB material to components; use underfill for large BGAs.

- Residue and Cleanliness

- Root Cause: Flux residues trapped under components affect surface impedance and cause leakage currents.

- Detection: Ionic contamination testing (ROSE test).

- Prevention: Specify strict wash protocols and cleanliness standards (IPC-5704).

Automotive Ethernet PCB layout validation and acceptance (tests and pass criteria)

Mitigating risks requires a robust validation plan. You cannot rely solely on the manufacturer's standard "pass" certificate for Automotive Ethernet PCB layout.

The following tests verify that the physical board meets the electrical and environmental requirements of the automotive industry.

- Impedance Verification (TDR)

- Objective: Confirm trace impedance matches 100 Ohms.

- Method: Time Domain Reflectometry on test coupons and actual boards.

- Acceptance Criteria: Mean impedance 100 Ohms ± 10%; no single point deviation > ± 15% (except at connector footprints).

- Insertion Loss Measurement

- Objective: Ensure signal strength is maintained over distance.

- Method: VNA (Vector Network Analyzer) measurement of S21 parameter.

- Acceptance Criteria: Loss < Specified limit (e.g., -0.5 dB/inch) up to the required bandwidth limit.

- Return Loss Measurement

- Objective: Verify minimal signal reflection.

- Method: VNA measurement of S11 parameter.

- Acceptance Criteria: < -20 dB at low frequencies; < -10 dB at Nyquist frequency.

- Mode Conversion (LCL/LCTL)

- Objective: Check for symmetry and immunity to noise conversion.

- Method: VNA measurement of Longitudinal Conversion Loss.

- Acceptance Criteria: Must meet IEEE 802.3bw (100BASE-T1) or 802.3bp (1000BASE-T1) limit lines.

- Thermal Shock / Cycling

- Objective: Verify barrel reliability and material stability.

- Method: 1000 cycles from -40°C to +125°C.

- Acceptance Criteria: < 5% change in resistance; no delamination or cracks.

- Interconnect Stress Test (IST)

- Objective: Accelerated testing of via reliability.

- Method: Rapid thermal cycling of specific coupons.

- Acceptance Criteria: Pass 500 cycles without open circuits.

- Surface Insulation Resistance (SIR)

- Objective: Detect electrochemical migration risks.

- Method: Bias voltage applied in high humidity (85°C/85% RH).

- Acceptance Criteria: Resistance > 100 MΩ after 168 hours.

- Solderability Test

- Objective: Ensure pads accept solder reliably.

- Method: Dip and look / Wetting balance test.

- Acceptance Criteria: > 95% coverage; smooth coating.

- Dimensional Stability

- Objective: Ensure board does not warp or shrink/stretch beyond tolerance.

- Method: Coordinate Measuring Machine (CMM).

- Acceptance Criteria: Bow and twist < 0.75%; registration within ± 3 mils.

- Microsection Analysis

- Objective: Verify stackup, plating thickness, and dielectric integrity.

- Method: Destructive cross-sectioning.

- Acceptance Criteria: Copper thickness meets IPC Class 3; no voids in laminate.

Automotive Ethernet PCB layout supplier qualification checklist (RFQ, audit, traceability)

To execute a successful Automotive Ethernet PCB layout, you need a supplier who understands the difference between a standard PCB and an automotive-grade high-speed board.

Use this checklist to vet potential partners or audit your current supply chain.

RFQ Inputs (What you must provide)

- Gerber Files (RS-274X): Complete set including drill files.

- IPC Netlist: For electrical test comparison.

- Stackup Drawing: Explicitly defining layer order, material type (brand/series), and thickness.

- Impedance Table: Listing layer, line width, spacing, and target impedance for every controlled net.

- Drill Drawing: Identifying plated vs. non-plated holes and backdrill locations.

- Fabrication Notes: Specifying IPC Class 3, automotive standards, and cleanliness requirements.

- Panelization Drawing: If specific array layout is needed for assembly.

- Test Coupon Request: Specifying if IPC standard coupons or custom in-circuit coupons are required.

- Volume Projections: EAU (Estimated Annual Usage) to determine tooling strategy.

Capability Proof (What they must demonstrate)

- Automotive Certification: Valid IATF 16949 certificate.

- Impedance Control: Demonstrated capability to hold ± 5% tolerance.

- Backdrilling: Proven process for controlled depth drilling with X-ray verification.

- Material Stock: Access to automotive-grade laminates (Isola, Rogers, Panasonic) without excessive lead time.

- VNA Testing: In-house capability to measure S-parameters (not just TDR).

- Cleanliness Lab: In-house ion chromatography or equivalent testing.

- AOI Capability: High-resolution inspection for fine lines (< 4 mil).

- Registration Accuracy: Laser direct imaging (LDI) capability for tight solder mask dams.

Quality System & Traceability

- Traceability: Ability to trace every PCB to the raw material lot and production date code.

- PFMEA: Process Failure Mode Effects Analysis specifically for high-speed boards.

- Control Plan: Detailed inspection points for critical characteristics (impedance, hole wall quality).

- MSA: Measurement System Analysis for their test equipment (Gage R&R).

- Non-Conforming Material: Clear quarantine and scrap procedure.

- Record Retention: Retention of quality records for 15+ years (typical automotive requirement).

Change Control & Delivery

- PCN Procedure: Strict adherence to Product Change Notification (no changes without approval).

- Buffer Stock: Willingness to hold safety stock for raw materials.

- Capacity Planning: Demonstrated capacity to handle surge demand.

- Logistics: Experience with automotive delivery schedules (JIT/Kanban).

- Packaging: ESD and moisture barrier packaging (MBB) compliant with J-STD-033.

- Disaster Recovery: Plan for production continuity in case of facility issues.

How to choose Automotive Ethernet PCB layout (trade-offs and decision rules)

Decisions in Automotive Ethernet PCB layout often involve balancing performance, cost, and manufacturability. There is rarely a "perfect" solution, only the right set of trade-offs for your specific application.

Here are the key decision rules to guide your architecture:

- Material Selection: FR4 vs. Low-Loss Materials

- If you prioritize cost and your speed is 100BASE-T1 (100 Mbps), choose high-Tg FR4. It is sufficient for short runs.

- If you prioritize signal integrity for 1000BASE-T1 or Multi-Gig over long distances (> 5 meters), choose Megtron 6 or Rogers. The reduced loss is necessary to meet channel budgets.

- Stackup: 4-Layer vs. 6-Layer+

- If you prioritize cost and have low component density, choose a 4-layer stackup.

- If you prioritize EMC performance, choose a 6-layer stackup. This allows for dedicated ground planes shielding the signal layers, significantly reducing radiated emissions.

- Vias: Through-Hole vs. HDI (Blind/Buried)

- If you prioritize manufacturing simplicity, use standard through-hole vias with backdrilling for critical nets.

- If you prioritize density and performance, use HDI (High Density Interconnect) with microvias. This eliminates stubs naturally but increases board cost by 20-40%.

- Connector Strategy: Integrated Magnetics vs. Discrete

- If you prioritize board space, choose connectors with integrated magnetics.

- If you prioritize layout flexibility and thermal management, choose discrete magnetics. This allows you to optimize the placement of the transformer relative to the PHY.

- Shielding: Unshielded (UTP) vs. Shielded (STP)

- If you prioritize weight and harness cost, choose UTP. This requires stricter PCB layout symmetry to reject noise.

- If you prioritize noise immunity in extremely harsh environments (e.g., near EV inverters), choose STP. This relaxes some PCB layout constraints but adds system weight.

- Test Points: On-Trace vs. Test Pads

- If you prioritize signal quality, avoid placing test points directly on high-speed differential pairs.

- If you prioritize debug capability, use small test pads but simulate the stub effect they create.

Automotive Ethernet PCB layout FAQ (cost, lead time, Design for Manufacturability (DFM) files, materials, testing)

Q: How does Automotive Ethernet PCB layout complexity affect unit cost? A: Complexity drives cost through material choice and layer count. Moving from standard FR4 to Megtron 6 can increase laminate cost by 2-3x, and adding backdrilling or HDI layers adds 15-30% to the fabrication cost due to extra process steps.

Q: What is the typical lead time for automotive-grade high-speed materials? A: Standard high-Tg FR4 is usually in stock. However, specialized low-loss materials like Isola Tachyon or Panasonic Megtron often have lead times of 4-6 weeks if not forecasted, so early engagement with your supplier is critical.

Q: What specific DFM files are needed for accurate impedance modeling? A: Beyond standard Gerbers, you must provide a stackup proposal that includes the specific dielectric brand and resin content (e.g., "Isola 370HR 1080 prepreg"). This allows the factory to calculate the exact press-out thickness and adjust trace widths for 100-ohm compliance.

Q: Can we use standard FR4 for 1000BASE-T1 Automotive Ethernet PCB layout? A: It is possible for very short traces (< 2-3 inches), but risky. Standard FR4 has higher loss and less consistent dielectric properties at high frequencies, which can lead to signal degradation and EMC failures in longer channels.

Q: What are the acceptance criteria for backdrilling depth? A: The remaining stub length should ideally be less than 10 mils (0.25mm). Manufacturers typically specify a "must not cut" layer (the internal signal layer) and a "must cut" depth, with a tolerance of ± 2-4 mils.

Q: How do you test for "Fiber Weave Effect" in production? A: You generally cannot test every board for FWE in mass production. Instead, you validate the design using "spread glass" materials or angled routing during the prototype phase and ensure the supplier locks the material construction in the control plan.

Q: What is the difference between IPC Class 2 and Class 3 for automotive Ethernet? A: Class 3 requires stricter annular rings, plating thickness, and visual standards, ensuring higher reliability under vibration and thermal stress. Automotive Ethernet PCBs should almost always be built to IPC Class 3 standards.

Q: Why is "mode conversion" critical for Automotive Ethernet PCB layout? A: Mode conversion measures how much of the differential signal (data) turns into common-mode noise (EMI). Since Automotive Ethernet uses unshielded cables, high mode conversion leads to immediate EMC test failures and radiated emissions issues.

Resources for Automotive Ethernet PCB layout (related pages and tools)

- Automotive Electronics PCB: Explore the broader context of automotive standards, including IATF 16949 requirements and safety-critical applications.

- High Speed PCB: Deep dive into the technical aspects of signal integrity, material selection, and routing techniques for gigabit data rates.

- PCB Stack Up: Learn how to design a symmetrical stackup that supports controlled impedance and reduces EMI risks.

- Impedance Calculator: Use this tool to estimate trace width and spacing for your 100-ohm differential pairs before finalizing your design.

- PCB Quality: Understand the inspection processes, including microsections and electrical testing, that guarantee your boards meet automotive specs.

Request a quote for Automotive Ethernet PCB layout (Design for Manufacturability (DFM) review + pricing)

Ready to validate your design? At APTPCB, we provide a comprehensive DFM review to catch impedance mismatches and manufacturability issues before you commit to tooling.

To get an accurate quote and DFM report, please send:

- Gerber Files: RS-274X or ODB++ format.

- Stackup & Impedance: Your desired layer count and 100-ohm target specifications.

- Material Requirements: Specific laminate preference (e.g., Megtron, Rogers, or High-Tg FR4).

- Volume & Timeline: Prototype quantity and estimated mass production ramp.

Click here to Request a Quote & DFM Review – Our engineering team will review your files and provide a detailed cost analysis and risk assessment within 24 hours.

Conclusion (next steps)

Mastering Automotive Ethernet PCB layout is about more than just routing traces; it is about managing the entire physical channel to ensure data integrity in a hostile environment. By defining clear specifications for impedance and materials, understanding the root causes of signal loss, and enforcing a rigorous validation plan, you can eliminate the most common risks associated with high-speed automotive networks. Use the checklist provided to vet your suppliers and ensure they have the capability to deliver consistent, reliable boards that keep your vehicles connected and safe.