Contents

- The Context: What Makes Grid Code Compliance Interface Quality Challenging

- The Core Technologies (What Actually Makes It Work)

- Ecosystem View: Related Boards / Interfaces / Manufacturing Steps

- Comparison: Common Options and What You Gain / Lose

- Reliability & Performance Pillars (Signal / Power / Thermal / Process Control)

- The Future: Where This Is Going (Materials, Integration, Ai/automation)

- Request a Quote / DFM Review for Grid Code Compliance Interface Quality (What to Send)

- Conclusion

Highlights

- Signal Integrity is Critical: Accurate grid sensing (LVRT/HVRT) depends on low-noise PCB layout and precise component placement.

- Isolation & Safety: Proper creepage, clearance, and material selection (CTI values) prevent catastrophic arc faults.

- Thermal Management: Interfaces often sit near hot power modules; the PCB must handle thermal cycling without delamination.

- Manufacturing Consistency: Automated inspection (AOI/SPI) ensures every unit meets the same strict grid standards.

The Context: What Makes Grid Code Compliance Interface Quality Challenging

Designing and manufacturing the interface for grid-tied equipment—whether for wind turbines, solar inverters, or battery energy storage systems (BESS)—is a balancing act between sensitivity and ruggedness. These boards must detect minute changes in grid frequency or voltage to trigger compliance modes like Low Voltage Ride Through (LVRT). However, they must do this while sitting inches away from high-power switching devices (IGBTs or SiC MOSFETs) that generate massive electromagnetic interference (EMI).

For APTPCB (APTPCB PCB Factory), the challenge lies in maintaining strict impedance control and cleanliness during fabrication. A minor deviation in the dielectric thickness or a small residue of flux can alter the sensing accuracy or compromise the high-voltage isolation. Furthermore, grid codes (such as IEEE 1547 or UL 1741) are unforgiving; a board that drifts over time due to poor material quality can cause an entire power plant to disconnect unexpectedly, leading to significant financial penalties.

The Core Technologies (What Actually Makes It Work)

Achieving high grid code compliance interface quality requires a fusion of advanced PCB fabrication techniques and precise assembly processes.

- Galvanic Isolation Techniques: The interface must separate the low-voltage control logic (DSP/FPGA) from the high-voltage grid connection. This is often achieved using wide-body optocouplers or digital isolators. The PCB layout must support these components with exact routing of isolation slots to prevent voltage creepage across the board surface.

- Precision Analog Layout: To measure grid voltage and current accurately, the PCB utilizes differential pair routing and dedicated analog ground planes. This minimizes the loop area, reducing the susceptibility to induced noise from nearby power switching.

- High-CTI Materials: The base material (laminate) matters significantly. Using FR4 with a high Comparative Tracking Index (CTI) ensures that the board resists electrical breakdown and tracking even in humid or polluted environments, which is essential for outdoor grid equipment.

- Heavy Copper & Thermal Vias: While the interface itself might be low power, it often routes drive signals or shares space with power rails. Heavy copper PCB traces and strategically placed thermal vias help dissipate heat, ensuring that thermal stress does not affect the accuracy of sensitive passive components.

Ecosystem View: Related Boards / Interfaces / Manufacturing Steps

The grid compliance interface does not exist in a vacuum. It is the central nervous system connecting the "muscle" (power modules) to the "brain" (central controller).

- The Power Stage: The interface board receives feedback from the power stage. If the power and energy PCB layout is poor, it will couple noise into the interface.

- The Gate Driver Board: Often, the compliance interface sends signals to a separate gate driver board. The connectors and cabling between these two must be impedance-matched to prevent signal reflection (ringing), which could cause false triggering.

- Assembly & Coating: Once assembled, these boards almost always require conformal coating. This step protects the sensitive sensing circuits from moisture and dust, which are inevitable in field deployments. A quality interface board is designed with "keep-out" zones to ensure coating does not interfere with connectors or test points.

Comparison: Common Options and What You Gain / Lose

Engineers often face trade-offs when specifying these interface boards. Should you use a standard 4-layer stackup or move to 6 layers for better noise immunity? Should you stick with standard FR4 or pay for high-performance dielectrics?

Below is a decision matrix to help navigate these choices based on practical outcomes.

Decision Matrix: Technical Choice → Practical Outcome

| Technical choice | Direct impact |

|---|---|

| 4-Layer vs. 6-Layer Stackup | 6-layer allows dedicated ground planes for analog and digital signals, significantly improving Signal-to-Noise Ratio (SNR) for grid sensing. |

| Standard FR4 vs. High CTI FR4 | High CTI (>600V) prevents carbon tracking in high-voltage areas, essential for meeting UL/IEC safety standards in compact designs. |

| HASL vs. ENIG Finish | ENIG provides a flatter surface for fine-pitch components (like DSPs) and better corrosion resistance than HASL for long-term reliability. |

| Class 2 vs. Class 3 Assembly | Class 3 ensures higher reliability through stricter criteria for solder fill and component alignment, critical for critical infrastructure equipment. |

Reliability & Performance Pillars (Signal / Power / Thermal / Process Control)

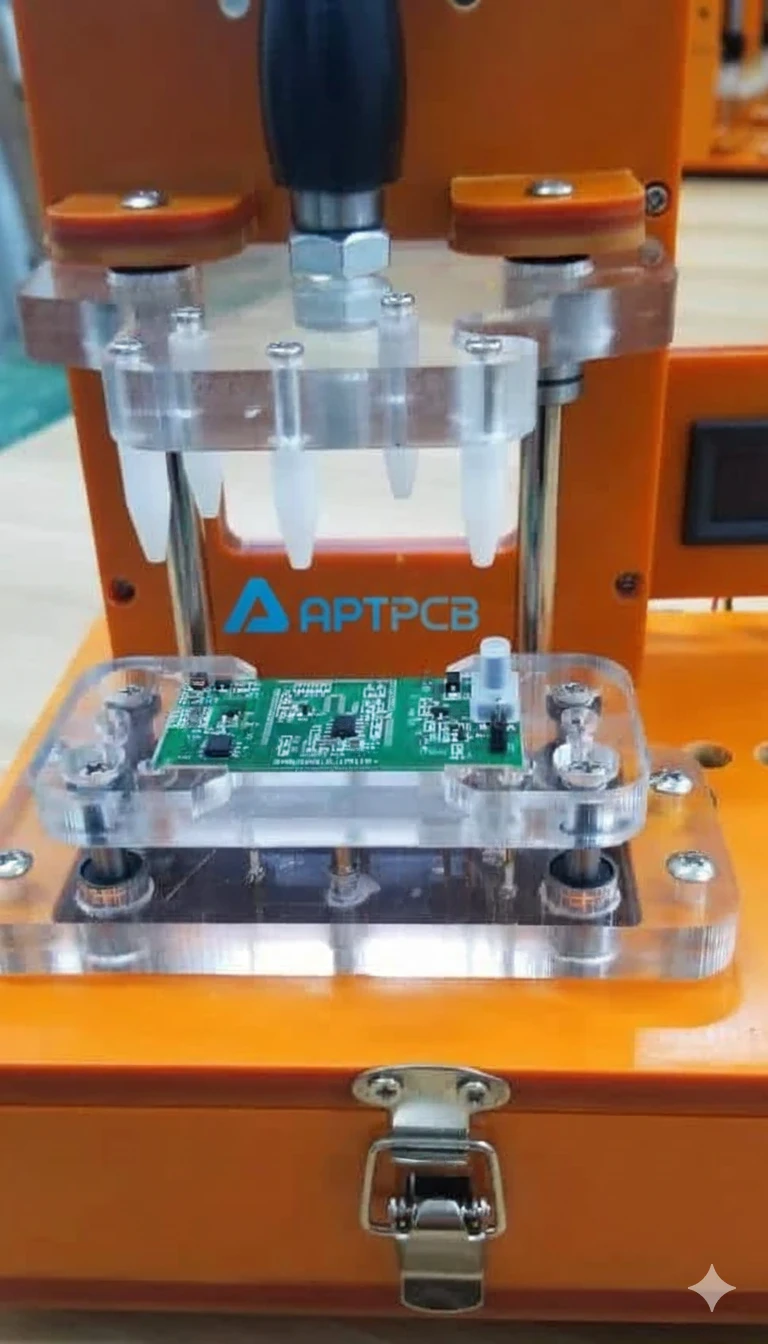

To ensure a grid compliance interface meets its targets, APTPCB emphasizes a rigorous verification process. It is not enough to just assemble the components; the board must be proven to withstand the electrical and physical stresses of the grid.

Key Verification Pillars

| Pillar | What to Verify | Acceptance Criteria |

|---|---|---|

| Signal Integrity | Analog sensing lines (Voltage/Current) | Noise floor < 10mV; No crosstalk affecting measurement accuracy. |

| Isolation | High Voltage to Low Voltage barrier | Pass Hi-Pot test at 2.5kV (or specific standard) with leakage < 1mA. |

| Thermal Stress | Solder joints under cycling | No cracking after 1000 cycles (-40°C to +125°C). |

| Cleanliness | Ionic contamination | < 1.56 µg/cm² NaCl equivalent to prevent electrochemical migration. |

Process control during PCB assembly is equally vital. Automated Optical Inspection (AOI) checks for missing or skewed components, while In-Circuit Testing (ICT) verifies that the passive components (resistors/capacitors) in the sensing network are within tolerance. A 1% resistor that is actually 5% off can cause a grid compliance failure.

The Future: Where This Is Going (Materials, Integration, Ai/automation)

As the grid becomes "smarter" and power electronics move toward Silicon Carbide (SiC) and Gallium Nitride (GaN), the demands on interface quality are shifting. Faster switching speeds mean more EMI, requiring even tighter layouts and better materials.

5-Year Performance Trajectory (Illustrative)

| Performance metric | Today (typical) | 5-year direction | Why it matters |

|---|---|---|---|

| Switching Frequency Handling | 20kHz - 50kHz | 100kHz - 500kHz | Higher frequencies reduce passive component size but increase EMI susceptibility, demanding advanced stackups. |

| Integration Level | Discrete sensing & control | Integrated Smart Modules | Combining sensing, control, and comms on one HDI board reduces assembly steps but increases complexity. |

| Data Reporting | Basic status flags | Real-time AI analytics | Interfaces will process data locally (Edge AI) to predict grid faults before they happen. |

Request a Quote / DFM Review for Grid Code Compliance Interface Quality (What to Send)

When you are ready to move your grid interface design from prototype to production, providing a complete data package is essential for accurate quoting and DFM analysis.

- Gerber Files: RS-274X format, including all copper layers, soldermask, and silkscreen.

- Fabrication Drawing: Specify IPC Class (2 or 3), material requirements (e.g., Tg 170, CTI > 600), and impedance control notes.

- Stackup Details: Define layer order and dielectric thickness if impedance is critical.

- BOM (Bill of Materials): Include manufacturer part numbers, especially for critical isolation components and precision resistors.

- Assembly Notes: Mention any special requirements like selective soldering for through-hole connectors or conformal coating specifications.

- Test Requirements: Define if ICT, FCT (Functional Circuit Test), or Hi-Pot testing is required at the factory.

- Volume & Lead Time: Estimated annual usage and target delivery dates.

Conclusion

Grid code compliance interface quality is not just a checkbox; it is the foundation of a stable and safe power grid. A well-engineered interface ensures that renewable energy sources and storage systems can interact seamlessly with the utility infrastructure, riding through faults and maintaining synchronization.

By focusing on robust materials, precise layout, and rigorous testing, manufacturers can avoid costly certification failures and field recalls. Whether you are designing for a small residential inverter or a massive utility substation, partnering with an experienced manufacturer like APTPCB ensures your interface boards meet the highest standards of reliability and performance.