Deciding to invest in Design for Manufacturability (DFM) and Design for Testability (DFT) is a strategic move that shifts quality control from a reactive "fix-it" phase to a proactive "prevent-it" phase. For buyers and product managers, understanding how to reduce pcba defects with dfm and dft is the most effective way to lower total costs and accelerate time-to-market. This guide provides the technical specifications and decision frameworks needed to align engineering designs with manufacturing capabilities.

Highlights

- Proactive Prevention: DFM identifies layout issues that cause bridging, tombstoning, and voids before production begins.

- Test Coverage: DFT ensures that if a defect occurs, it is detectable via ICT or functional testing rather than escaping to the field.

- Cost Reduction: Fixing a defect at the design stage costs 10x less than at the assembly stage and 100x less than in the field.

- Supplier Alignment: Clear specifications regarding stencil design and reflow profiles are critical for complex components like BGAs and QFNs.

Key Takeaways

Before diving into the technical details, here is a summary of how these methodologies directly impact your bottom line and product reliability.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Primary Goal | Ensure the product can be built consistently with high yield. | Ensure the product can be verified accurately and quickly. |

| Defect Focus | Prevents defects from happening (e.g., solder bridges). | Catches defects that do happen (e.g., open circuits). |

| Key Deliverable | Optimized pad layouts, thermal relief, component spacing. | Test points, JTAG access, scan chains. |

| ROI Driver | Higher First Pass Yield (FPY), less rework. | Lower field failure rate, faster diagnosis. |

How to Reduce PCBA Defects with DFM and DFT: Scope, Decision Context, and Success Criteria

The scope of reducing defects extends beyond the assembly line; it begins at the schematic and layout phase. When asking how to reduce pcba defects with dfm and dft, buyers must understand that they are purchasing a process capability, not just a commodity board.

Decision Context

Buyers often face a trade-off between upfront engineering time and downstream production speed. Skipping DFM checks to rush a prototype often results in "unbuildable" boards or high scrap rates during volume production. The decision context involves evaluating the complexity of the Printed Circuit Board Assembly (PCBA). A simple board with large passives may require minimal DFM, but a high-density interconnect (HDI) board with Ball Grid Arrays (BGAs) requires rigorous analysis.

Success Criteria

To validate that your DFM and DFT efforts are working, track these metrics:

- First Pass Yield (FPY): The percentage of boards that pass all tests without rework. A target of 98%+ is standard for mature products.

- Test Coverage: The percentage of nets and components accessible by automated testing. High DFT aims for 90%+ coverage.

- False Fail Rate: The frequency with which good boards are flagged as bad due to poor test limits or unstable fixtures.

- Engineering Change Orders (ECOs): A reduction in ECOs related to assembly issues indicates successful DFM.

Specifications to Define Upfront (Before You Commit)

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 (typical), higher as needed | Drives cost, yield, and routing margin | Stackup + DFM report |

| Min trace/space | 4/4 mil (typical) | Impacts yield and lead time | DRC + fab capability |

| Via strategy | Through vias vs VIPPO vs microvias | Affects assembly reliability | Microsection + IPC criteria |

| Surface finish | ENIG/OSP/HASL | Impacts solderability and flatness | COC + solderability tests |

| Solder mask | Matte green (default) | AOI readability and bridging risk | AOI trial + mask registration |

| Test | Flying probe / ICT / FCT | Coverage vs cost trade-off | Coverage report + fixture plan |

| Acceptance class | IPC Class 2 / 3 | Defines defect limits | Drawing notes + inspection report |

| Lead time | Standard vs expedited | Schedule risk | Quote + capacity confirmation |

To effectively implement DFM and DFT, specific requirements must be included in your data package. Ambiguity here leads to assumptions on the factory floor, which is a primary source of defects.

1. DFM Data Requirements

Provide your Contract Manufacturer (CM) with more than just Gerber files.

- IPC Class Selection: Explicitly state if the board is IPC-A-610 Class 2 (Standard) or Class 3 (High Reliability). This dictates solder volume and alignment criteria.

- Component Footprints: Require verification of footprints against the Bill of Materials (BOM). Mismatches between the physical part and the land pattern are common DFM failures.

- Panelization Strategy: Define the panel array. Poor panelization can cause stress fractures in ceramic capacitors during depanelization (breaking the boards apart).

- Solder Mask Dams: Specify minimum solder mask dams between pads (typically 4 mils) to prevent solder bridging on fine-pitch ICs.

2. DFT Data Requirements

DFT is often an afterthought, leading to expensive "bed of nails" fixtures that cannot reach critical nets.

- Test Point Accessibility: Mandate that all critical nets have a test point on the bottom side of the PCB. This allows for single-sided In-Circuit Testing (ICT), which is significantly cheaper.

- Test Point Clearance: Specify a minimum clearance (e.g., 50 mils) between test points and tall components to prevent probe damage.

- JTAG/Boundary Scan: For complex digital boards, ensure the JTAG chain is routed and accessible. This allows testing of connections between chips without physical probes.

- Netlist: Always supply an IPC-356 netlist. This file allows the manufacturer to compare the Gerber connectivity against the schematic connectivity.

Related resources

Key Risks (Root Causes, Early Detection, Prevention)

Understanding specific defect types helps in prioritizing DFM checks. The most challenging defects often occur under bottom-terminated components like QFNs (Quad Flat No-lead) and BGAs.

1. Voiding in QFN and BGA Components

Voids are air pockets trapped within the solder joint. Excessive voiding reduces thermal conductivity and mechanical strength.

- Risk: High-power QFNs overheating due to poor thermal transfer through voided solder.

- Prevention (DFM): Implement qfn reflow best practices to reduce voids. This involves window-paning the solder paste aperture on the thermal pad. Instead of printing one large block of paste (which traps gas), print a grid of smaller squares (e.g., 50-70% coverage). This allows outgassing channels for volatiles to escape during reflow.

2. BGA Solder Defects (Bridging and Opens)

BGAs are difficult because the joints are hidden.

- Risk: Head-in-Pillow (HiP) defects where the solder ball rests on the paste but does not coalesce.

- Prevention (DFM/Process): Strict bga voiding control: stencil, reflow, and x-ray criteria are required.

- Stencil: Use electro-polished stencils with trapezoidal apertures to ensure good paste release.

- Reflow: Optimize the soak zone profile. If the flux burns off too early, oxidation prevents wetting.

- X-Ray Criteria: Define pass/fail limits. For IPC Class 2, voids typically must be less than 25% of the ball area.

3. Tombstoning

This occurs when a small passive component stands up on one end during reflow.

- Root Cause: Uneven wetting forces, often caused by one pad being connected to a large ground plane (acting as a heat sink) while the other is on a thin trace.

- Prevention (DFM): Use thermal relief connections on ground pads. This restricts heat flow, ensuring both pads reach reflow temperature simultaneously.

4. Shadowing

In wave soldering or selective soldering, large components can block the solder wave from reaching smaller components behind them.

- Prevention (DFM): Maintain specific spacing rules based on the direction of travel through the wave solder machine.

Validation & Acceptance (Tests and Pass Criteria)

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| Electrical continuity | Flying probe / fixture | 100% nets tested; no opens/shorts | E-test report |

| Critical dimensions | Measurement | Meets drawing tolerances | Inspection record |

| Plating / fill integrity | Microsection | No voids/cracks beyond IPC limits | Microsection photos |

| Solderability | Wetting test | Acceptable wetting; no de-wet | Solderability report |

| Warpage | Flatness measurement | Within spec (e.g., ≤0.75%) | Warpage record |

| Functional validation | FCT | All cases pass; log stored | FCT logs |

How do you prove that the DFM and DFT efforts were successful? You must establish a validation plan that correlates with your NPI assembly goals.

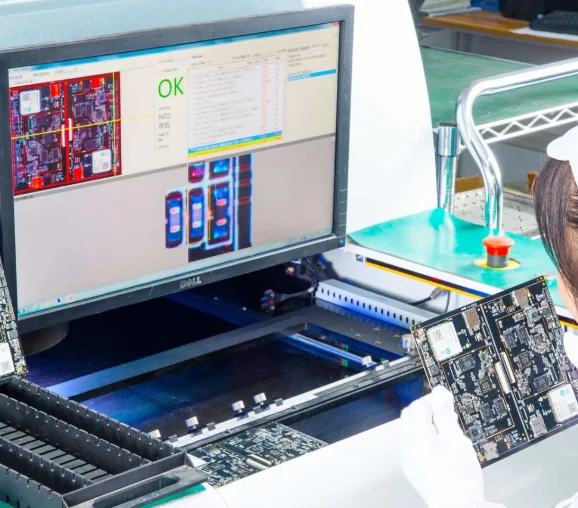

Automated Optical Inspection (AOI)

AOI is the first line of defense. It uses cameras to check for component presence, polarity, skew, and solder quality.

- Pass Criteria: No missing parts, polarity marks aligned, solder fillets meet IPC standards.

- Limitation: Cannot see beneath BGAs or QFNs.

X-Ray Inspection (Axi)

Essential for BGA and QFN validation.

- Pass Criteria: bga voiding control: stencil, reflow, and x-ray criteria must be met. Voids <25%, consistent ball shape, no bridging.

- Application: 100% inspection for prototypes; sample inspection for mass production.

- Learn More: X-Ray Inspection Services

In-Circuit Test (ICT) and Flying Probe

This is where DFT pays off.

- ICT: Uses a fixture (bed of nails) to test all nets simultaneously. Fast, but fixture cost is high. Requires test points defined in DFT.

- Flying Probe: Uses robotic arms to probe points. No fixture required, but slower. Ideal for prototypes.

- Pass Criteria: All passive values within tolerance; no shorts/opens on active nets.

Functional Circuit Test (FCT)

The final validation step. The board is powered up and made to perform its actual function.

- Pass Criteria: Device boots, firmware loads, I/O ports respond.

Supplier Qualification Checklist (RFQ, Audit, Traceability)

When selecting a partner to help you learn how to reduce pcba defects with dfm and dft, use this checklist.

1. Engineering Capabilities

- Does the supplier perform a mandatory DFM review before tooling?

- Do they provide a detailed DFM report (not just a "pass/fail") highlighting risks like acid traps or slivers?

- Can they suggest alternative footprints to improve yield?

- See DFM Guidelines for what to expect.

2. Process Control

- Do they have Solder Paste Inspection (SPI) machines inline? (SPI prevents 70% of Solder defects).

- Do they have X-Ray capabilities in-house?

- Can they handle qfn reflow best practices to reduce voids (e.g., vacuum reflow or profile optimization)?

3. Traceability and Quality System

- Is the facility ISO 9001 or IATF 16949 certified?

- Do they offer component-level traceability (linking specific batches of parts to specific serial numbers)?

- Review their Quality System.

How to Choose How to Reduce PCBA Defects with DFM and DFT (Trade-Offs and Decision Rules)

Not every board requires the same level of DFM/DFT intensity. Use these decision rules to balance cost and risk.

Scenario a: Simple Consumer Electronics (Low Cost, High Volume)

- Strategy: Focus on DFM to maximize yield and minimize cycle time.

- DFT: Minimal. Rely on AOI and functional sampling.

- Trade-off: Accepting a slightly higher field failure rate to keep unit costs low.

Scenario B: Medical/automotive (High Reliability, Medium Volume)

- Strategy: Aggressive DFM and DFT.

- DFT: 100% ICT and 100% Functional Test.

- Trade-off: Higher NRE (Non-Recurring Engineering) costs for fixtures and programming, but near-zero field failures.

- Specifics: Strict adherence to bga voiding control: stencil, reflow, and x-ray criteria.

Scenario C: Rapid Prototyping

- Strategy: "Soft" DFM. Fix only "showstoppers" that prevent assembly.

- DFT: Flying probe testing (no fixture cost).

- Trade-off: Higher per-unit test time, but faster delivery.

FAQ (Cost, Lead Time, DFM Files, Materials, Testing)

1. Does adding DFM/DFT requirements increase the quote price? Yes, initially. Engineering time and test fixture fabrication (NRE) add upfront costs. However, this reduces the unit price by improving yield and eliminating rework, often resulting in a lower total project cost.

2. How much time does a DFM review add to the lead time? Typically 1–2 days. A thorough DFM review happens before materials are ordered. This short delay prevents weeks of delay caused by discovering unbuildable features later.

3. Can DFM fix a bad circuit design? No. DFM ensures the board can be built, not that it will work. If the schematic has logic errors, the board will be manufactured perfectly but fail functionally.

4. What is the difference between DFM and DFA? DFM (Design for Manufacturing) usually refers to PCB fabrication (etching, drilling). DFA (Design for Assembly) refers to the population of components (soldering, clearances). In practice, "DFM" is often used to cover both.

5. Do I need ICT if I have a Functional Test? Ideally, yes. ICT tells you which component failed (e.g., "Resistor R5 is open"). Functional testing only tells you that the board failed (e.g., "Device won't boot"). ICT makes repair and diagnosis much faster.

6. How do materials affect DFM? Material selection (e.g., High Tg FR4) affects how the board expands during reflow. Mismatched CTE (Coefficient of Thermal Expansion) between the component and the board is a major cause of solder fatigue.

7. What is the best way to communicate DFM notes? Include a "Read Me" text file or PDF in your Gerber zip file. Explicitly list special requirements like "Do not X-out arrays" or "Mask plug vias at U1."

Request a Quote / DFM Review for How to Reduce PCBA Defects with DFM and DFT (What to Send)

Ready to optimize your PCBA for mass production? Send your data package to us for a comprehensive DFM review.

Checklist for Quote Request:

- Gerber Files (RS-274X): Copper layers, solder mask, silkscreen, drill files, paste layers.

- Bill of Materials (BOM): Excel format with Manufacturer Part Numbers (MPN) and Reference Designators.

- Centroid File (Pick and Place): X-Y coordinates and rotation data.

- Assembly Drawings: PDF showing component locations and polarity marks.

- Test Requirements: Description of desired test coverage (ICT, FCT, Burn-in).

Glossary (Key Terms)

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: layout rules that reduce defects. | Prevents rework, delays, and hidden cost. |

| AOI | Automated Optical Inspection used to find solder/assembly defects. | Improves coverage and catches early escapes. |

| ICT | In-Circuit Test that probes nets to verify opens/shorts/values. | Fast structural test for volume builds. |

| FCT | Functional Circuit Test that powers the board and checks behavior. | Validates real function under load. |

| Flying Probe | Fixtureless electrical test using moving probes on pads. | Good for prototypes and low/medium volume. |

| Netlist | Connectivity definition used to compare design vs manufactured PCB. | Catches opens/shorts before assembly. |

| Stackup | Layer build with cores/prepreg, copper weights, and thickness. | Drives impedance, warpage, and reliability. |

| Impedance | Controlled trace behavior for high-speed/RF signals (e.g., 50Ω). | Avoids reflections and signal integrity failures. |

| ENIG | Electroless Nickel Immersion Gold surface finish. | Balances solderability and flatness; watch nickel thickness. |

| OSP | Organic Solderability Preservative surface finish. | Low cost; sensitive to handling and multiple reflows. |

Conclusion (Next Steps)

Learning how to reduce pcba defects with dfm and dft is an investment in the longevity and reputation of your product. By defining clear specifications for stencil design, reflow profiles, and test accessibility, you transform the manufacturing process from a black box into a controlled, predictable science.

Start by engaging your manufacturing partner early in the design phase. A collaborative review of qfn reflow best practices to reduce voids and bga voiding control: stencil, reflow, and x-ray criteria will save significant time and capital. Prioritize transparency in your data package, validate with rigorous testing, and choose a supplier that views quality as a shared responsibility.