An industrial-grade PMBus monitor PCB serves as the central nervous system for modern power management, enabling real-time telemetry, voltage sequencing, and fault logging in harsh environments. Unlike consumer electronics, industrial power systems face high electromagnetic interference (EMI), thermal cycling, and voltage transients that can corrupt sensitive digital communication. Designing a reliable Power Management Bus (PMBus) interface requires strict adherence to physical layer specifications, robust layout techniques, and rigorous validation.

APTPCB (APTPCB PCB Factory) specializes in manufacturing high-reliability boards where signal integrity is non-negotiable. This guide provides the engineering specifications, layout rules, and troubleshooting steps necessary to deploy a robust PMBus monitoring solution.

industrial-grade PMBus monitor PCB quick answer (30 seconds)

Successful deployment of an industrial-grade PMBus monitor PCB relies on minimizing noise coupling and ensuring signal integrity across the bus.

- Capacitance Limit: Keep total bus capacitance (traces + device pins) under 400pF to maintain rise time specifications; use bus buffers for larger loads.

- Grounding: Always route a dedicated ground return trace parallel to SDA and SCL lines to minimize loop area and inductance.

- Pull-up Resistors: Place pull-up resistors (typically 1kΩ–4.7kΩ) close to the master or the last device, verified against bus capacitance to ensure logic high levels are reached within timing limits.

- Isolation: Use digital isolators (optocouplers or capacitive) when crossing power domains to prevent ground loops and protect low-voltage logic.

- Protection: Implement series termination resistors (22Ω–47Ω) near the driver to dampen reflections and ESD protection diodes near connectors.

- Validation: Always enable Packet Error Checking (PEC) in firmware to detect data corruption in noisy industrial environments.

When industrial-grade PMBus monitor PCB applies (and when it doesn’t)

Understanding the operational context ensures you do not over-engineer simple systems or under-engineer critical ones.

When it applies (Critical Necessity)

- Server and Data Center Power: When managing multi-phase VRMs (Voltage Regulator Modules) requiring dynamic voltage scaling (AVS) and precise current balancing.

- Industrial Motor Drives: Systems requiring real-time monitoring of DC bus voltage, temperature, and fault status to prevent catastrophic motor failure.

- Telecom Rectifiers: Applications needing remote management, efficiency logging, and "black box" fault recording via non-volatile memory.

- Automotive Systems: Automotive-grade PMBus monitor PCB designs for EV battery management systems (BMS) where ISO 26262 functional safety is required.

- Complex FPGA/ASIC Boards: Sequencing multiple voltage rails (0.8V, 1.2V, 1.8V, 3.3V) with strict timing requirements during power-up and power-down.

When it doesn’t apply (Overkill or Unsuitable)

- Simple Consumer Electronics: Low-power devices using fixed LDOs or standalone buck converters where telemetry adds unnecessary cost.

- High-Speed Data Transmission: PMBus (typically 100kHz, 400kHz, or 1MHz) is too slow for transferring large data payloads; use SPI or PCIe instead.

- Extremely Long Cable Runs: Standard PMBus is not differential; for distances over 1-2 meters in noisy environments, RS-485 or CAN bus is superior.

- Ultra-Low Cost Toys: The overhead of a PMBus controller and associated firmware development is not justifiable.

industrial-grade PMBus monitor PCB rules and specifications (key parameters and limits)

The physical layer of an industrial-grade PMBus monitor PCB must be robust. Adhering to these parameters prevents the majority of communication failures.

| Rule | Recommended Value/Range | Why it matters | How to verify | If ignored |

|---|---|---|---|---|

| Trace Impedance | Not strictly controlled, but aim for ~50-70Ω | While not a transmission line at 100kHz, consistent geometry reduces susceptibility. | Impedance Calculator | Inconsistent edges and potential ringing. |

| Bus Capacitance | < 400pF total | High capacitance slows down signal rise times, causing timing violations. | LCR meter or simulation. | "Stuck" bus or inability to reach Logic High (V_IH). |

| Pull-up Resistors | 1kΩ to 4.7kΩ (Calc. required) | Determines the current drive and rise time. Stronger (lower R) for high C. | Oscilloscope (measure rise time). | Weak pull-up: Slow edges. Strong pull-up: Driver sink failure. |

| Series Resistors | 22Ω to 47Ω | Dampens ringing and limits current during transient events. | BOM review. | Signal overshoot/undershoot; EMI emissions. |

| Trace Width | 6 mil to 10 mil | Wider traces reduce resistance but increase capacitance. | Gerber viewer. | Voltage drop on long runs (V_IL issues). |

| Ground Reference | Solid Plane or Parallel Trace | Minimizes loop area for return current, reducing inductive noise pickup. | Layout review. | High susceptibility to EMI; data corruption. |

| Via Count | Minimize (0-2 per net) | Vias add capacitance (~1pF each) and impedance discontinuities. | Drill drawing check. | Marginal signal integrity degradation. |

| Isolation Creepage | > 2.5mm (depends on voltage) | Prevents arcing between high-voltage power stage and low-voltage logic. | CAD Design Rules (DRC). | Safety hazard; catastrophic controller failure. |

| PEC Support | Enabled | CRC-8 checksum verifies data integrity per packet. | Firmware/Logic Analyzer. | Silent data corruption leads to wrong voltage settings. |

| Alert Line (SMBALERT#) | Wired-AND (Open Drain) | Allows slaves to interrupt master immediately upon fault. | Schematic check. | Delayed response to critical faults (e.g., Over-Temp). |

industrial-grade PMBus monitor PCB implementation steps (process checkpoints)

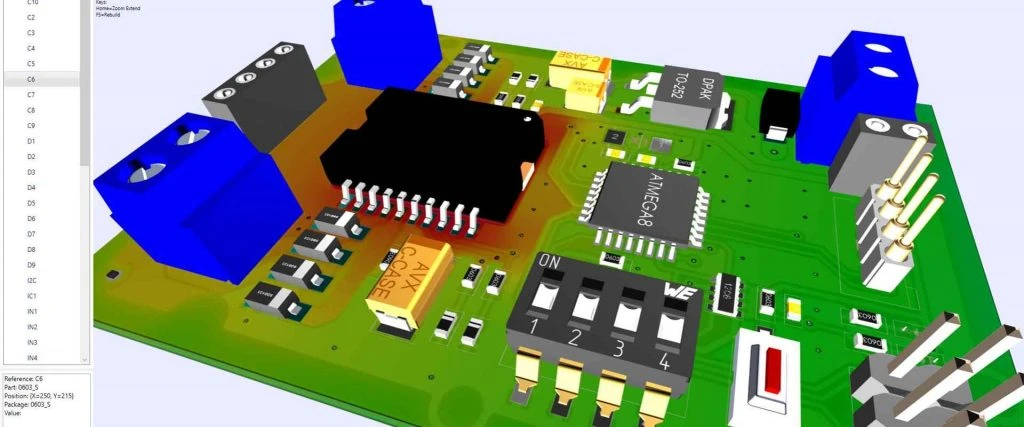

Designing an industrial-grade PMBus monitor PCB involves a systematic approach from schematic to assembly.

Schematic Architecture & Address Allocation

- Action: Map out all PMBus slaves (POL converters, sensors, fans). Assign unique 7-bit addresses.

- Key Parameter: Check for address conflicts. Use resistor straps to set addresses if devices support it.

- Acceptance: No duplicate addresses; address map document created.

Stackup Definition & Material Selection

- Action: Select a multi-layer laminated structure that allows for a solid ground reference immediately adjacent to the signal layer.

- Key Parameter: Dielectric thickness (distance to ground).

- Acceptance: Signal layers 1 or N have adjacent GND planes on layers 2 or N-1.

Component Placement & Partitioning

- Action: Group PMBus devices logically. Place the master controller centrally or near the connector. Place pull-up resistors at the far end or near the master (depending on topology).

- Key Parameter: Trace length. Keep total bus length as short as possible.

- Acceptance: Digital isolators placed exactly at the barrier between High Voltage and Low Voltage zones.

Routing the Bus (SDA, SCL, ALERT#)

- Action: Route SDA and SCL as a pair (but not tightly coupled differential). Route a GND trace alongside them ("guard trace") if a continuous plane is not available.

- Key Parameter: Loop area.

- Acceptance: No routing over split planes; no routing near high dV/dt switch nodes.

Noise Immunity & Protection

- Action: Add TVS diodes at board-to-board connectors. Add decoupling capacitors (0.1µF) at every active device power pin.

- Key Parameter: Clamping voltage of TVS.

- Acceptance: ESD protection present on all external interfaces.

Design for Manufacturing (DFM) Review

- Action: Verify minimum trace widths and clearances for the chosen copper weight. Industrial boards often use heavy copper for power, requiring larger clearances.

- Key Parameter: Etch factor and solder mask expansion.

- Acceptance: DFM check passed with APTPCB engineering team.

Prototype Assembly & Validation

- Action: Assemble the PMBus monitor PCB assembly. Use an oscilloscope to capture eye diagrams or rise/fall times of the bus.

- Key Parameter: Rise time < 300ns (for 400kHz mode).

- Acceptance: Clean square waves; ACK bits received correctly; PEC validates 100% of packets.

industrial-grade PMBus monitor PCB troubleshooting (failure modes and fixes)

Even with robust design, issues can arise in the field. Use this guide to diagnose PMBus monitor PCB failures.

1. Bus Stuck Low (Lockup)

- Symptom: SCL or SDA line is held at 0V continuously. Communication halts.

- Causes: A slave device is in an unknown state; a power-down sequence failed; a short circuit to ground.

- Checks: Measure resistance to ground on SDA/SCL (power off). Check if a slave is holding the bus (clock stretching indefinitely).

- Fix: Power cycle the system. Implement "Bus Recovery" sequence in the master (toggle SCL 9 times to release SDA).

- Prevention: Use PMBus devices with built-in timeout features.

2. Intermittent NACK (No Acknowledge)

- Symptom: Master sends command, but slave does not respond (NACK). Happens randomly.

- Causes: Noise spikes on the clock line interpreted as extra bits; voltage drop on ground reference (Ground Shift).

- Checks: Inspect ground potential difference between Master and Slave. Look for crosstalk from nearby switching regulators.

- Fix: Improve grounding (wide straps). Add small filter capacitors (10-20pF) to SCL/SDA (caution: watch total capacitance).

- Prevention: Strict separation of noisy power grounds and quiet signal grounds.

3. Data Corruption (PEC Errors)

- Symptom: Data is received, but values are nonsensical (e.g., reading 500V on a 12V rail).

- Causes: EMI coupling into the bus; weak pull-up resistors causing slow rise times.

- Checks: Verify rise time is sharp. Check if corruption correlates with high-load switching events.

- Fix: Lower the pull-up resistor value (strengthen the pull-up). Shield the cable or traces.

- Prevention: Enable PEC (Packet Error Checking) to discard corrupted packets automatically.

4. Address Conflict

- Symptom: Two devices respond simultaneously, causing bus contention (weird voltage levels like 1.5V).

- Causes: Incorrect resistor strap values; manufacturing error in component placement.

- Checks: Isolate devices one by one. Check resistor tolerances (1% vs 5%).

- Fix: Correct the address strap resistors.

- Prevention: Use 1% tolerance resistors for address strapping. Verify BOM against schematic.

How to choose industrial-grade PMBus monitor PCB (design decisions and trade-offs)

When specifying an industrial-grade PMBus monitor PCB, several strategic decisions dictate the board's reliability and cost.

1. PCB Material Selection For standard industrial environments, high-Tg FR4 (Tg > 170°C) is sufficient. However, if the monitor PCB is integrated directly onto a high-power module, thermal expansion becomes a concern. In these cases, matching the CTE (Coefficient of Thermal Expansion) is critical to prevent solder joint cracking on small passives.

2. Isolation Strategy

- Non-Isolated: Acceptable only if the controller and power stage share the same ground reference (e.g., Point-of-Load converters on a motherboard).

- Isolated: Mandatory for off-line power supplies (AC-DC) or when communicating between different ground domains. Digital isolators (like the ADuM or ISO series) are preferred over optocouplers for PMBus due to speed and aging characteristics.

3. Connector Reliability The physical interface is often the weak point. For PMBus monitor PCB assembly, avoid cheap pin headers. Use latching connectors or direct board-to-board headers with gold plating to prevent fretting corrosion caused by industrial vibration.

4. Copper Weight While the PMBus signals are low current, the PCB often carries power. Using heavy copper PCB technology (2oz or 3oz) helps with thermal management of the power stage but requires careful etching control for the fine PMBus signal lines. APTPCB recommends a minimum of 8-10 mil trace width for signal lines on heavy copper layers to ensure etch consistency.

industrial-grade PMBus monitor PCB FAQ (cost, lead time, Design for Manufacturing (DFM) files, stackup, impedance, IPC class)

Q: Can I run PMBus traces on inner layers? A: Yes, and it is often preferred. Running traces on inner layers (stripline) between two ground planes provides excellent EMI shielding. Ensure you account for the slightly higher capacitance per inch compared to outer layers (microstrip).

Q: What is the maximum distance for an industrial PMBus connection? A: The standard does not specify distance, only capacitance (400pF). In practice, 30-50cm is safe. For longer runs (e.g., across a cabinet), use PMBus buffers or range extenders (like the PCA9600) to drive higher capacitance loads.

Q: How does "Automotive-grade PMBus monitor PCB" differ from industrial? A: Automotive grade requires adherence to AEC-Q100 standards for components and often ISO 26262 for safety. The PCB itself may require higher thermal cycling endurance and stricter cleanliness standards to prevent dendritic growth.

Q: Should I use 100kHz or 400kHz? A: Use 100kHz for maximum robustness and noise immunity in harsh industrial environments. Use 400kHz only if you need high throughput for downloading large logs or updating firmware rapidly.

Q: Do I need impedance control for PMBus? A: Strictly speaking, no. PMBus is not a transmission line protocol at these speeds. However, maintaining consistent trace width and spacing helps predict capacitance and reduces reflections.

industrial-grade PMBus monitor PCB glossary (key terms)

| Term | Definition |

|---|---|

| PMBus | Power Management Bus. An open standard protocol based on I2C for controlling power converters. |

| SMBus | System Management Bus. The parent protocol of PMBus, defining electrical characteristics and timing. |

| PEC | Packet Error Checking. A CRC-8 byte added to the end of a transmission to verify data integrity. |

| SDA | Serial Data Line. The bidirectional line used to transfer data bits. |

| SCL | Serial Clock Line. The clock signal generated by the master to synchronize data transfer. |

| ALERT# | An interrupt line used by slave devices to signal a fault (e.g., Over-Voltage) to the master immediately. |

| Clock Stretching | A mechanism where a slave holds SCL low to pause the master while it processes data. |

| V_IH / V_IL | Voltage Input High / Low. The voltage thresholds that define logic 1 and logic 0. |

| NACK | No Acknowledge. A bit sent by the receiver to indicate it did not receive the byte or cannot process it. |

| Zone Interlock | A protection scheme where devices communicate faults to shut down upstream power sources. |

Request a quote for industrial-grade PMBus monitor PCB (Design for Manufacturing (DFM) review + pricing)

Ready to manufacture your industrial-grade PMBus monitor PCB? APTPCB provides comprehensive DFM reviews to ensure your layout meets strict impedance and isolation requirements before production begins.

Please prepare the following for an accurate quote:

- Gerber Files: RS-274X format preferred.

- Stackup Diagram: Specify layer count, copper weight, and dielectric materials.

- BOM (Bill of Materials): If requesting turnkey assembly, include manufacturer part numbers.

- Special Requirements: Note any impedance control, heavy copper, or specific IPC class requirements (Class 2 or 3).

Conclusion (next steps)

Designing an industrial-grade PMBus monitor PCB requires moving beyond basic connectivity to focus on resilience. By strictly managing bus capacitance, implementing robust grounding strategies, and utilizing features like PEC, engineers can build power management systems that withstand the electrical noise and thermal stress of industrial environments. Whether you are prototyping a server backplane or a motor drive controller, APTPCB delivers the manufacturing precision required to turn your high-reliability design into reality.