Achieving RF front-end low noise PCB compliance is the critical gateway between a functional prototype and a market-ready wireless product. In high-frequency applications—such as 5G infrastructure, automotive radar, and satellite communications—the PCB itself is an active component. Even minor deviations in manufacturing tolerances, material properties, or assembly cleanliness can degrade the Noise Figure (NF), ruin Signal-to-Noise Ratio (SNR), and cause regulatory failures (FCC/ETSI).

This guide provides a direct engineering checklist to ensure your designs meet strict manufacturing and performance standards. APTPCB (APTPCB PCB Factory) specializes in fabricating these sensitive interconnects, ensuring that the physical board matches your simulation data.

RF front-end low noise PCB compliance quick answer (30 seconds)

If you are rushing to validate a design or troubleshoot a failure, check these critical compliance boundaries first.

- Material Dielectric Loss (Df): For Low Noise Amplifiers (LNAs) above 2 GHz, ensure Df is < 0.003 (e.g., Rogers 4350B or similar) to minimize insertion loss which directly adds to the noise figure.

- Copper Roughness: Specify VLP (Very Low Profile) or HVLP copper foil. Standard ED copper roughness creates a "skin effect" drag that increases resistive loss and noise.

- Impedance Tolerance: Standard ±10% is often insufficient for RF front-ends; specify ±5% or ±7% for 50Ω traces to prevent reflections (Return Loss) that degrade signal integrity.

- Grounding Vias: Place stitching vias along RF traces at intervals less than λ/20 (wavelength/20) to prevent parasitic resonance and EMI leakage.

- Surface Finish: Use ENIG (Electroless Nickel Immersion Gold) or Immersion Silver. HASL creates uneven surfaces that alter impedance and can cause Passive Intermodulation (PIM).

- Cleanliness: Ionic contamination must be strictly controlled (IPC-TM-650). Residues absorb moisture and alter the dielectric constant, detuning sensitive RF filters.

When RF front-end low noise PCB compliance applies (and when it doesn’t)

Understanding when to enforce strict compliance rules helps balance cost and performance. Not every board requires aerospace-grade RF specifications.

Strict compliance is required when:

- Signal Frequency > 1 GHz: Skin depth becomes shallow, and dielectric losses dominate.

- Low Signal Amplitude: The input signal is near the thermal noise floor (e.g., GPS receivers, radio telescopes).

- Complex Modulation: High-order QAM schemes (Wi-Fi 6/7, 5G) require high SNR; PCB noise directly reduces throughput.

- Regulatory Certification: The device must pass strict radiated emission and immunity tests (EMC/EMI).

- Active Antenna Systems (AAS): Phased arrays where phase consistency between channels is paramount.

Strict compliance is less critical when:

- Low-Frequency Analog/Digital: Sub-100 MHz signals are forgiving of standard FR4 materials and ±10% tolerances.

- High-Power Transmit Stages: While impedance matters, thermal management often takes precedence over the absolute lowest noise floor (unlike the receive side).

- Simple Key Fobs/Toys: Short-range, low-data-rate devices often function well with standard manufacturing processes.

- Digital Logic Sections: The digital control section of a mixed-signal board does not need the expensive materials used for the RF front-end section.

RF front-end low noise PCB compliance rules and specifications (key parameters and limits)

To achieve RF front-end low noise PCB compliance, you must translate performance goals into manufacturing specifications. Use this table to define your fabrication notes.

| Rule / Parameter | Recommended Value / Range | Why it matters | How to verify | Consequence if ignored |

|---|---|---|---|---|

| Impedance Control | 50Ω ±5% (or specific differential) | Matches LNA/Antenna impedance to minimize reflections. | TDR (Time Domain Reflectometry) coupons. | High VSWR, signal reflection, reduced range. |

| Dielectric Constant (Dk) Tolerance | ±0.05 or better | Ensures consistent phase velocity and filter tuning. | Material datasheet & batch certification. | Detuned filters, phase errors in arrays. |

| Copper Surface Roughness | < 1.0 µm (VLP/HVLP) | Reduces conductor loss due to skin effect at high frequencies. | SEM analysis or microsection. | Increased insertion loss, higher Noise Figure. |

| Solder Mask on RF Traces | Remove (Keep-out) or LPI < 10µm | Solder mask has high Df; covering traces increases loss. | Visual inspection / Gerber review. | Unpredictable impedance drop, higher loss. |

| Via Stitching Pitch | < λ/20 of highest freq | Creates a Faraday cage to block external noise. | DRC (Design Rule Check) in CAD. | EMI susceptibility, crosstalk coupling. |

| Layer-to-Layer Registration | ±3 mil (0.075mm) or better | Critical for coupled lines and broadside coupling. | X-Ray inspection. | Mismatched differential pairs, mode conversion. |

| Plated Through Hole (PTH) Wall | > 20µm copper (Class 3) | Ensures thermal reliability and low resistance grounding. | Cross-section analysis. | Ground loops, thermal failure during operation. |

| Etch Factor / Trace Width | ±0.5 mil (0.013mm) | Width directly dictates impedance. | AOI (Automated Optical Inspection). | Impedance discontinuity, signal reflection. |

| Surface Finish | ENIG, Immersion Ag, ENEPIG | Flatness for fine pitch; conductivity for skin effect. | X-Ray Fluorescence (XRF). | PIM issues, soldering defects on fine components. |

| Weave Effect (Fiberglass) | Spread Glass (e.g., 1067, 1078) | Prevents periodic loading variations on traces. | Material spec sheet. | Skew in differential pairs, timing jitter. |

| Ionic Cleanliness | < 1.56 µg/cm² NaCl eq. | Prevents electrochemical migration and leakage. | ROSE test / Ion Chromatography. | Long-term drift, corrosion, noise floor rise. |

RF front-end low noise PCB compliance implementation steps (process checkpoints)

Following a structured workflow ensures that RF front-end low noise PCB compliance is built into the product, not just tested at the end.

- Define the Frequency Budget:

- Action: Identify the highest operating frequency and the required Noise Figure budget.

- Check: Does the loss budget allow for FR4, or is Rogers/Teflon material required?

- Select the Stackup:

- Action: Design a layer stack that places RF signals adjacent to solid ground planes. Avoid routing RF signals across split planes.

- Check: Verify the stackup with your fabricator to ensure material availability and press thickness.

- Calculate Impedance with Manufacturing Data:

- Action: Use a solver that accounts for etchback and solder mask.

- Check: Use an impedance calculator and confirm the geometry with the fab house.

- Layout for Low Noise:

- Action: Keep RF traces short. Place the LNA as close to the antenna connector as possible. Use curved traces or mitered bends to reduce reflections.

- Check: Verify clearance (3W rule) to digital lines to prevent switching noise coupling.

- Grounding Strategy:

- Action: Flood unused areas with ground. Stitch top and bottom grounds aggressively near the RF path.

- Check: Ensure no "island" grounds exist; every copper pour must be grounded.

- DFM Review:

- Action: Send preliminary Gerbers to APTPCB for a "Design for Manufacturing" check.

- Check: Resolve minimum trace width/spacing violations before final release.

- Fabrication & Test Coupon Generation:

- Action: Request impedance coupons on the production panel.

- Check: Ensure the coupons match the actual traces in the board (same layer, same width).

- Assembly & Reflow:

- Action: Use a reflow profile compatible with the laminate (especially for hybrid stackups).

- Check: Inspect for voiding in ground pads of QFN/LGA components (X-Ray).

- Final Compliance Testing:

- Action: Measure S-parameters (S11, S21) and Noise Figure.

- Check: Compare results against the simulation model.

RF front-end low noise PCB compliance troubleshooting (failure modes and fixes)

When a board fails RF front-end low noise PCB compliance testing, the root cause is often hidden in the fabrication details.

Symptom: High Noise Figure (NF) / Low Sensitivity

- Possible Cause: High insertion loss due to wrong material or rough copper.

- Check: Verify if the correct laminate was used (check markings). Look for solder mask over RF lines where it should be removed.

- Fix: Switch to VLP copper; remove solder mask from critical RF traces.

Symptom: High VSWR / Poor Return Loss (S11)

- Possible Cause: Impedance mismatch. Trace width over-etched or dielectric thickness incorrect.

- Check: Measure TDR coupons. Check if the reference ground plane is interrupted by a via or slot.

- Fix: Adjust trace width in next spin; ensure continuous ground reference.

Symptom: Spurious Emissions / Oscillation

- Possible Cause: Poor grounding or internal feedback loops.

- Check: Inspect via stitching density. Look for coupling between input and output of high-gain amplifiers.

- Fix: Add more stitching vias; increase isolation distance; use shielding cans.

Symptom: Passive Intermodulation (PIM)

- Possible Cause: Ferromagnetic materials (Nickel) in the signal path or poor solder joints.

- Check: Did you use HASL finish? Are there cold solder joints?

- Fix: Switch to Immersion Silver or OSP. Ensure robust solder reflow.

Symptom: Signal Drift over Temperature

- Possible Cause: High CTE (Coefficient of Thermal Expansion) or unstable Dk.

- Check: Is the material suitable for the operating temperature range?

- Fix: Use microwave PCB materials with stable Dk/temperature characteristics.

Symptom: Digital Noise in RF Spectrum

- Possible Cause: Power supply coupling or crosstalk.

- Check: Analyze the PDN (Power Distribution Network). Is the RF power clean?

- Fix: Improve filtering (ferrite beads); separate analog and digital grounds physically (net-ties).

How to choose RF front-end low noise PCB compliance (design decisions and trade-offs)

Deciding on the level of RF front-end low noise PCB compliance involves balancing performance against cost and lead time.

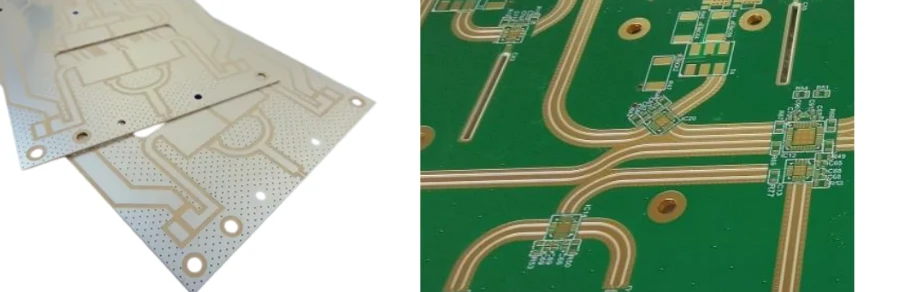

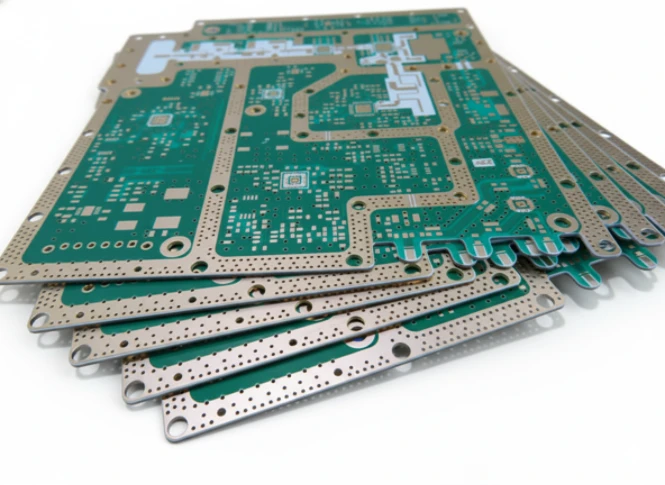

1. Material Selection: Hybrid vs. Pure RF

- Pure RF (e.g., All Rogers): Best performance, consistent Dk, lowest loss. Trade-off: High cost, harder to process (drilling wear).

- Hybrid (Rogers + FR4): RF layer on top, FR4 for digital/power/mechanical support. Trade-off: Complex stackup design, potential warping issues (CTE mismatch), but significantly cheaper.

2. Surface Finish: ENIG vs. Immersion Silver

- ENIG: Excellent shelf life, flat surface. Trade-off: Nickel layer is magnetic and lossy at very high frequencies; can cause PIM.

- Immersion Silver: Best for loss and PIM. Trade-off: Tarnishes easily; requires careful handling and storage.

3. Via Technology: Through-hole vs. Microvias

- Through-hole: Standard cost. Trade-off: Via stubs act as antennas/filters at high frequencies, ruining signal integrity.

- HDI (Microvias/Buried/Blind): Eliminates stubs, improves density. Trade-off: Higher manufacturing cost and complexity.

4. Tolerance Stringency

- Standard (±10%): No extra cost. Trade-off: Acceptable for <1GHz or short traces.

- Precision (±5%): Surcharge applies. Trade-off: Essential for >2GHz or long transmission lines to maintain RF front-end low noise PCB compliance.

RF front-end low noise PCB compliance FAQ (cost, lead time, common defects, acceptance criteria, Design for Manufacturability (DFM) files)

Q: How much does strict RF front-end low noise PCB compliance increase PCB cost? A: It typically increases bare board cost by 30% to 100% compared to standard FR4 boards. The primary drivers are specialized high-frequency laminates (Rogers/Taconic), tighter impedance testing (TDR), and advanced surface finishes.

Q: What is the typical lead time for these compliant boards? A: Standard lead time is 8–12 days. Quick-turn options (3–5 days) are available if materials are in stock. Hybrid stackups may require 1–2 extra days for lamination cycles.

Q: What are the most common defects found during acceptance testing? A: The most frequent issues are impedance deviations (due to etching variation), solder mask misregistration covering pads, and poor plating in vias leading to intermittent grounding.

Q: Do I need to provide specific test points for compliance verification? A: Yes. You should include test coupons or specific test points at the input/output of the RF chain. For testing and quality assurance, TDR coupons on the panel rails are standard.

Q: What files are required for a DFM review of an RF front-end design? A: Submit Gerber files (RS-274X), a detailed stackup drawing specifying material types and dielectric thicknesses, drill files, and an IPC netlist. Clearly mark "Controlled Impedance" traces.

Q: Can I use standard FR4 for a 2.4 GHz Low Noise Amplifier? A: It is possible for short traces and consumer-grade performance. However, FR4 has a loose Dk tolerance and higher loss. For strict RF front-end low noise PCB compliance, a high-performance FR4 (like Isola FR408) or a hybrid stackup is recommended.

Q: How does copper roughness affect my compliance results? A: At frequencies above 1-2 GHz, current flows in the outer "skin" of the copper. Rough copper increases the path length, increasing resistance and insertion loss. Specifying VLP copper is a low-cost way to improve performance.

Q: What is the acceptance criteria for RF via plating? A: According to IPC-6012 Class 3 (often used for RF), average copper plating thickness in the hole should be 25µm (1 mil) to ensure low resistance and thermal robustness, preventing ground loops.

Q: How do I specify "cleanliness" for my RF PCB? A: Specify "Ionic Contamination per IPC-TM-650 2.3.25" with a limit typically < 1.56 µg/cm² of NaCl equivalent. This ensures no conductive residues remain that could alter RF performance.

Q: Does APTPCB support hybrid stackups for cost reduction? A: Yes, we frequently manufacture hybrid boards combining RF materials (top layer) with FR4 (inner/bottom layers) to optimize cost while maintaining RF front-end low noise PCB compliance.

Resources for RF front-end low noise PCB compliance (related pages and tools)

- Materials: RF Rogers PCB Materials – Compare Dk and Df values.

- Design Tools: Impedance Calculator – Estimate trace widths before layout.

- Manufacturing: Microwave PCB Capabilities – Detailed specs for high-frequency boards.

- Quality: Testing & Quality Control – How we verify your specs.

RF front-end low noise PCB compliance glossary (key terms)

| Term | Definition | Relevance to Compliance |

|---|---|---|

| LNA (Low Noise Amplifier) | An active component that amplifies weak signals with minimal added noise. | The PCB layout must not degrade the LNA's native Noise Figure. |

| Noise Figure (NF) | A measure of degradation of the Signal-to-Noise Ratio (SNR). | Lower is better. PCB loss directly adds to NF (dB for dB). |

| Insertion Loss | The loss of signal power as it travels through the PCB trace. | Must be minimized via low-loss materials and smooth copper. |

| Return Loss (S11) | The loss of power in the signal returned/reflected by a discontinuity. | High return loss (good matching) is required for compliance. |

| Dk (Dielectric Constant) | The measure of a material's ability to store electrical energy. | Determines trace width for 50Ω and signal propagation speed. |

| Df (Dissipation Factor) | A measure of the energy lost as heat in the dielectric material. | Lower Df materials are required for low noise designs. |

| Skin Effect | The tendency of high-frequency current to flow near the surface of the conductor. | Makes copper surface roughness a critical compliance factor. |

| PIM (Passive Intermodulation) | Generation of interfering signals caused by non-linearities (e.g., rust, loose contacts). | A major failure mode in high-power RF front-ends. |

| TDR (Time Domain Reflectometry) | A measurement technique used to determine the impedance of PCB traces. | The standard method for verifying impedance compliance. |

| Hybrid Stackup | A PCB stackup using different materials (e.g., Rogers + FR4). | Balances RF performance with mechanical strength and cost. |

Request a quote for RF front-end low noise PCB compliance

Ready to move your design from simulation to reality? APTPCB provides comprehensive DFM reviews to catch impedance mismatches and material conflicts before production begins.

To get an accurate quote and DFM report, please provide:

- Gerber Files: RS-274X format.

- Stackup Drawing: Specify material type (e.g., Rogers 4350B), copper weight, and total thickness.

- Impedance Requirements: List target impedance (e.g., 50Ω) and layers.

- Volume: Prototype quantity vs. mass production estimates.

Conclusion (next steps)

Achieving RF front-end low noise PCB compliance is not about guessing; it is about rigorous adherence to material science and manufacturing physics. By controlling dielectric loss, copper roughness, and grounding strategies, you ensure your device performs exactly as simulated. Whether you are building a 5G base station or a precision radar module, following these specifications will minimize noise figures and maximize signal integrity.