Security Protocol PCB quick answer (30 seconds)

Designing a Security Protocol PCB requires balancing high-speed signal integrity for encryption data with physical defenses against intrusion. Whether for a Network Security PCB or a hardware security module (HSM), the manufacturing process must adhere to stricter tolerances than standard consumer electronics.

- Impedance Control: Critical protocols (PCIe, Ethernet, proprietary encryption buses) require strict impedance matching, typically ±5% to ±10%, to prevent packet loss and timing errors.

- Anti-Tamper Meshes: High-security designs often utilize active copper meshes on outer or inner layers with trace widths/spacing as tight as 0.10mm (4mil) to detect physical drilling or probing.

- Buried Vias: Use buried vias to hide critical security keys and sensitive nets within the internal layers, making them inaccessible to external probing.

- Material Selection: Low-loss materials are essential for Protocol Analyzer PCB designs operating at high frequencies to minimize signal attenuation and skew.

- Cleanliness Standards: Ionic contamination must be minimized to prevent leakage currents that could trigger false tamper alarms in sensitive active mesh circuits.

- Validation: 100% Netlist testing and Time Domain Reflectometry (TDR) are mandatory to verify that the physical board matches the security design intent.

When Security Protocol PCB applies (and when it doesn’t)

Not every board requires security-grade fabrication. Understanding when to apply these rigorous standards helps optimize cost and performance.

When to use Security Protocol PCB standards:

- Hardware Security Modules (HSM): Devices storing cryptographic keys require physical anti-tamper meshes and buried signal layers.

- Network Security Appliances: High-throughput firewalls and VPN gateways need low-loss materials to handle encrypted traffic without latency.

- LIDAR and Perimeter Systems: LIDAR Security PCB designs require precise timing and noise immunity to process time-of-flight data accurately.

- Defense and Aerospace: Systems requiring compliance with FIPS 140-2 or similar standards mandate specific physical security features on the PCB.

- Protocol Bridges: A Protocol Bridge PCB translating between secure and insecure domains must ensure isolation and prevent crosstalk.

When standard PCB fabrication is sufficient:

- General IoT Sensors: Unless the sensor handles classified data, standard FR4 and IPC Class 2 specs are usually sufficient.

- Consumer Peripherals: Basic keyboards or mice (non-encrypted) do not justify the cost of buried vias or tamper meshes.

- Prototyping Logic: Early-stage breadboarding where security features are handled in software rather than hardware.

- Low-Speed Control Boards: Simple power management boards often do not require high-speed impedance control or anti-tamper features.

Security Protocol PCB rules and specifications (key parameters and limits)

To ensure a Security Protocol PCB functions correctly and resists attacks, specific manufacturing rules must be defined in the fabrication notes.

| Rule | Recommended Value/Range | Why it matters | How to verify | If ignored |

|---|---|---|---|---|

| Impedance Tolerance | ±5% (High Speed) or ±10% (Standard) | Ensures signal integrity for encrypted data streams. | TDR (Time Domain Reflectometry) Coupons. | Data corruption, packet loss, communication failure. |

| Tamper Mesh Trace Width | 0.10mm - 0.127mm (4-5 mil) | Detects physical intrusion (drilling/peeling). | AOI (Automated Optical Inspection). | Attackers can bypass the mesh without triggering alarms. |

| Tamper Mesh Spacing | 0.10mm - 0.127mm (4-5 mil) | Prevents bridging or bypassing the mesh. | AOI and Electrical Test (E-Test). | Short circuits or undetected physical probing. |

| Dielectric Constant (Dk) | Stable (e.g., 3.4 - 3.8 for high speed) | Affects signal propagation speed and impedance. | Material datasheet & Stackup analysis. | Impedance mismatch, timing skew in high-speed protocols. |

| Via Type | Blind and/or Buried | Hides sensitive nets from external access. | X-Ray Inspection. | Critical signals are exposed to surface probing attacks. |

| Copper Weight | 0.5 oz - 1 oz (Inner layers) | Thinner copper allows for finer etch lines (meshes). | Microsection analysis. | Inability to etch fine tamper meshes; short circuits. |

| Solder Mask Color | Black or Matte Black | Obscures traces visually to hinder reverse engineering. | Visual Inspection. | Traces are easily visible, aiding attackers in mapping the circuit. |

| Layer Count | 4 - 12+ Layers | Allows burying sensitive signals between ground planes. | Stackup verification. | EMI leakage and exposed security signals. |

| Ionic Contamination | < 1.56 µg/cm² NaCl eq. | Prevents leakage currents in high-impedance tamper circuits. | ROSE Test / Ion Chromatography. | False tamper alarms due to humidity/contamination. |

| Skew Budget | < 5ps per inch | Critical for differential pairs in Protocol Analyzer PCB. | Simulation & TDR. | Data synchronization errors in high-speed interfaces. |

Security Protocol PCB implementation steps (process checkpoints)

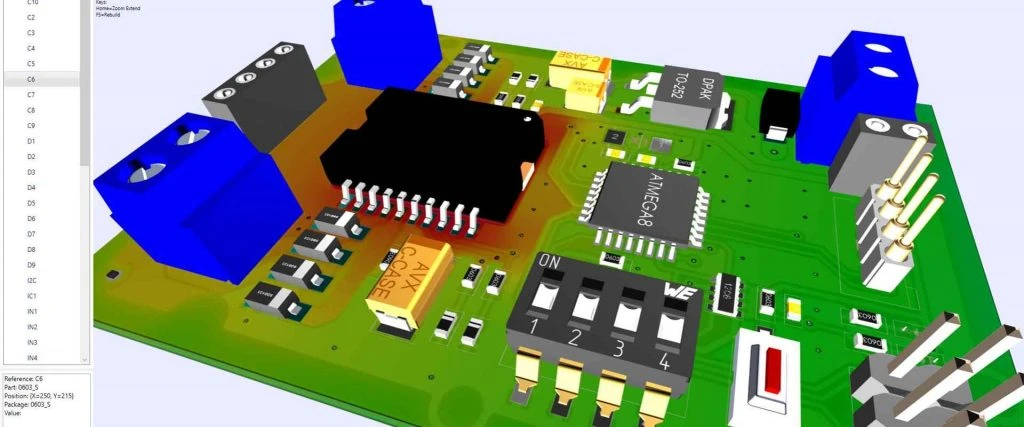

Successful deployment of a Security Protocol PCB involves strict process control from design to final assembly. APTPCB (APTPCB PCB Factory) recommends following these checkpoints to ensure security compliance.

- Define Security Boundary: Identify which area of the PCB contains critical secrets (keys, processors). This area requires the highest density of protection (meshes, buried vias).

- Select Material & Stackup: Choose materials based on signal speed. For a Network Security PCB running 10GbE+, use low-loss laminates (like Megtron 6 or Rogers). Define a stackup that places sensitive signals on inner layers (stripline configuration).

- Design Anti-Tamper Mesh: Generate a serpentine pattern on the outer layers (and potentially inner layers) surrounding the secure zone. Ensure the pattern is randomized or optimized to prevent easy bypassing.

- Route High-Speed Interfaces: Route differential pairs for protocols (PCIe, DDR) with strict length matching. Ensure these do not cross split planes to maintain return paths.

- DFM Review: Submit Gerber files for a DFM check. Specifically ask the fabricator to check if the fine lines of the tamper mesh are within etch capabilities for the chosen copper weight.

- Fabrication with Controlled Depth: If using blind vias, ensure the drill depth is precise to avoid connecting to unintended layers.

- Electrical Testing (100%): Perform "flying probe" or "bed of nails" testing on 100% of nets. For security boards, open/short testing thresholds should be strict to detect micro-defects in the tamper mesh.

- Impedance Validation: Use TDR to measure the actual impedance of test coupons. This confirms that the dielectric thickness and trace width meet the design specs.

- Visual Obfuscation: Apply opaque solder mask (usually black) and remove unnecessary silkscreen labels that identify component values or functions.

- Final Quality Audit: Verify that no repair wires (jumpers) are present, as these are unacceptable in high-security hardware.

Security Protocol PCB troubleshooting (failure modes and fixes)

Issues in Security Protocol PCB production often manifest as signal integrity problems or false security alarms.

Symptom: False Tamper Alarms (Active Mesh Triggering)

- Causes: Ionic contamination causing leakage current; micro-fractures in fine mesh traces; over-etching.

- Checks: Perform ionic cleanliness testing. Check microsections for trace integrity.

- Fix: Improve board washing process. Increase trace width slightly if impedance allows.

- Prevention: Use high-quality etching processes and specify strict cleanliness limits.

Symptom: High Bit Error Rate (BER) on Encrypted Links

- Causes: Impedance mismatch; excessive crosstalk; dielectric loss too high.

- Checks: Review TDR reports. Check eye diagrams on the Protocol Analyzer PCB.

- Fix: Respin PCB with corrected stackup or lower-loss material.

- Prevention: Simulate signal integrity during the design phase; use controlled impedance fabrication.

Symptom: EMI Failure in Perimeter Security PCB

- Causes: Incomplete return paths; noisy power delivery; exposed high-speed clocks.

- Checks: Near-field scanning. Verify ground stitching vias.

- Fix: Add shielding cans; improve grounding on the next revision.

- Prevention: Bury high-speed clocks between ground planes (stripline).

Symptom: Intermittent Connection in Rigid-Flex Security Designs

- Causes: Stress on vias near the bend radius; conductor cracking.

- Checks: Microsection of the flex area.

- Fix: Move vias away from bend zones; use teardrops on pads.

- Prevention: Follow strict rigid-flex design guidelines regarding bend radii and coverlay openings.

Symptom: Skew Issues in Differential Pairs

- Causes: Fiber weave effect (glass weave causing speed variation); length mismatch.

- Checks: TDR skew measurement.

- Fix: Rotate design 10 degrees on the panel (zig-zag routing) or use spread glass.

- Prevention: Specify "spread glass" or "flat glass" materials for high-speed differential pairs.

How to choose Security Protocol PCB (design decisions and trade-offs)

Choosing the right architecture for a Security Protocol PCB involves trading off cost against security level and signal performance.

Rigid vs. Rigid-Flex for Security

- Rigid PCBs: Lower cost, standard manufacturing. To secure them, you often need a separate metal enclosure or potting compound.

- Rigid-Flex PCBs: Allow the PCB to fold around the sensitive electronics, creating a "3D" tamper envelope. This offers higher security but significantly increases manufacturing cost and lead time.

Standard FR4 vs. Low-Loss Materials

- Standard FR4: Sufficient for low-speed security keys and basic Perimeter Security PCB logic. Cheap and readily available.

- Low-Loss (Rogers/Megtron): Required for Network Security PCB designs handling high-speed traffic (10Gbps+). More expensive and harder to process (lamination cycles), but necessary for signal integrity.

Active vs. Passive Tamper Mesh

- Passive Mesh: A simple ground shield. Easy to manufacture but offers limited protection against sophisticated probing.

- Active Mesh: Continuous circuits monitored by the processor. If the circuit is broken (drilled) or shorted, the device wipes its keys. Requires finer trace/space capabilities (HDI technology) and cleaner processing.

Blind/Buried Vias vs. Through-Hole

- Through-Hole: Cheapest, but exposes all signals to the bottom side of the board, making probing easy.

- Blind/Buried: Essential for high security. Buried vias keep signals entirely internal. Increases lamination cycles and cost by 30-50%.

Security Protocol PCB FAQ (cost, lead time, common defects, acceptance criteria, Design for Manufacturability (DFM) files)

1. How does adding a tamper mesh affect the PCB cost? Adding a fine-pitch tamper mesh often pushes the board into HDI (High Density Interconnect) classification due to tight trace/space requirements (e.g., 3/3 mil or 4/4 mil). This can increase the bare board cost by 20-40% due to lower yields and stricter inspection.

2. What is the typical lead time for a Security Protocol PCB? Standard prototypes take 5-7 days. However, designs with blind/buried vias or special materials for LIDAR Security PCB applications typically require 10-15 working days due to sequential lamination cycles.

3. Can APTPCB manufacture PCBs with active anti-tamper meshes? Yes, APTPCB specializes in security equipment PCB manufacturing, capable of etching fine lines down to 3 mil for active mesh layers and verifying them with AOI.

4. What files are needed for a DFM review of a security board? You must provide Gerber files (RS-274X), a drill file, an IPC-356 netlist (crucial for validating the mesh), and a stackup drawing specifying impedance and material requirements.

5. How do you test the integrity of buried security traces? We use IPC-356 netlist testing. The flying probe tester verifies continuity and isolation based on the netlist extracted from your CAD data, ensuring buried nets are not shorted to planes.

6. What is the best surface finish for security PCBs? ENIG (Electroless Nickel Immersion Gold) is preferred. It provides a flat surface for fine-pitch components (BGA) often used in security controllers and offers excellent corrosion resistance for long-term reliability.

7. How do I prevent "fiber weave effect" in high-speed security protocols? Specify "spread glass" (e.g., 1067, 1078 style) in your fabrication notes. This ensures a more uniform dielectric constant for differential pairs, reducing timing skew.

8. Can you hide the vias to prevent reverse engineering? Yes, using "via-in-pad" technology with epoxy filling and capping makes the vias invisible on the surface, complicating attempts to trace the circuit visually.

9. What are the acceptance criteria for tamper meshes? The mesh must be free of "mouse bites" (nicks) that reduce the trace width by more than 20%, and there must be no shorts. Cleanliness is paramount to prevent electrochemical migration.

10. Do you support ITAR or sensitive data handling? For specific compliance requirements regarding data handling and facility access, please contact our engineering team directly to discuss your project's security needs.

11. Why is impedance control critical for a Protocol Bridge PCB? A Protocol Bridge PCB often connects two different high-speed standards. Mismatched impedance causes reflections that degrade the signal eye diagram, leading to data errors that can compromise the security handshake.

12. What is the difference between a Protocol Analyzer PCB and a standard sniffer? A Protocol Analyzer PCB is designed with extremely low-intrusiveness. It uses high-impedance taps and precise length matching to monitor signals without distorting them, requiring high-speed PCB design techniques.

Resources for Security Protocol PCB (related pages and tools)

- Security Equipment PCB Manufacturing: Specific capabilities for surveillance, access control, and encrypted hardware.

- High-Speed PCB Design: Essential reading for maintaining signal integrity in protocol analyzers and network appliances.

- Multilayer PCB Stackups: Understanding how to configure layers for buried vias and stripline routing.

- HDI PCB Capabilities: Technology required for fine-pitch anti-tamper meshes and microvias.

Security Protocol PCB glossary (key terms)

| Term | Definition |

|---|---|

| Active Mesh | A continuous serpentine trace pattern monitored by a circuit; breaking it triggers a security event (e.g., key erasure). |

| Buried Via | A via connecting internal layers only, not visible from the outer surfaces. Critical for hiding signals. |

| Differential Pair | Two complementary signals used to transmit data with high noise immunity (e.g., USB, PCIe). |

| FIPS 140-2 | A US government computer security standard used to approve cryptographic modules. |

| HSM | Hardware Security Module; a physical computing device that safeguards and manages digital keys. |

| Impedance | The opposition to AC current flow in a trace, determined by width, thickness, and dielectric height. |

| LIDAR | Light Detection and Ranging; requires PCBs with precise timing and low noise for perimeter security. |

| Netlist Test | Electrical test that verifies the physical board matches the logical connections defined in the CAD design. |

| Skew | The time difference between the arrival of two signals (e.g., the P and N of a differential pair). |

| Stripline | A PCB trace routed on an inner layer, sandwiched between two ground planes for shielding. |

| TDR | Time Domain Reflectometry; a measurement technique used to verify the characteristic impedance of PCB traces. |

| Via-in-Pad | Placing a via directly in a component pad, plated over, to save space and improve thermal/electrical performance. |

Request a quote for Security Protocol PCB

Ready to manufacture your secure hardware? APTPCB provides a comprehensive DFM review to ensure your anti-tamper designs and impedance specs are manufacturable before production begins.

Please include the following for an accurate quote:

- Gerber Files: RS-274X format preferred.

- Stackup Drawing: Specify material type (e.g., FR4, Rogers), layer order, and impedance requirements.

- Drill File: Clearly indicate blind/buried via depths.

- Netlist: IPC-356 format for 100% electrical validation.

- Volume: Prototype quantity vs. mass production estimates.

Conclusion (next steps)

Successfully manufacturing a Security Protocol PCB requires more than just standard fabrication; it demands a partner who understands the nuances of signal integrity, material stability, and physical security features. From precise impedance control for Network Security PCB interfaces to the fine-line etching required for anti-tamper meshes, every detail matters. By following the rules and specifications outlined above, you can ensure your hardware meets the rigorous demands of modern security infrastructure.