Surface Mount Technology (SMT) stencil design is the engineering process of defining aperture geometries, foil thickness, and material properties to control the precise volume of solder paste deposited on a Printed Circuit Board (PCB). This critical manufacturing step dictates the success of the soldering process, as approximately 60% to 70% of all SMT assembly defects originate from incorrect printing parameters. A robust design balances the physical limitations of the stencil foil with the wetting requirements of the electronic components.

Key Takeaways

- Primary Function: The stencil acts as a volumetric control tool; the volume of paste deposited equals the aperture area multiplied by the foil thickness.

- Critical Metric (Area Ratio): The Area Ratio (AR) must be ≥ 0.66 for standard processes to ensure the paste releases from the stencil rather than sticking to the walls.

- Critical Metric (Aspect Ratio): The Aspect Ratio (width/thickness) must be ≥ 1.5 to prevent clogging.

- Misconception: A 1:1 aperture-to-pad ratio is rarely correct; most designs require a 10% to 20% global reduction to prevent bridging and solder balls.

- Validation Tip: Use Solder Paste Inspection (SPI) data to verify that transfer efficiency exceeds 80% during the First Article Inspection (FAI).

- Material Choice: Stainless steel (SUS304) is the industry standard, but fine-pitch designs (< 0.5mm) require fine-grain steel or nickel-electroformed foils.

- Decision Rule: If the component pitch is ≤ 0.4mm, you must use a nanocoating or flux-repellent surface treatment to maintain print definition.

Contents

- What It Really Means (Scope & Boundaries)

- Metrics That Matter (How to Evaluate It)

- How to Choose (Selection Guidance by Scenario)

- Implementation Checkpoints (Design to Manufacturing)

- Common Mistakes (and the Correct Approach)

- FAQ (Cost, Lead Time, Materials, Testing, Acceptance Criteria)

- Glossary (key terms)

- Conclusion (next steps)

What It Really Means (Scope & Boundaries)

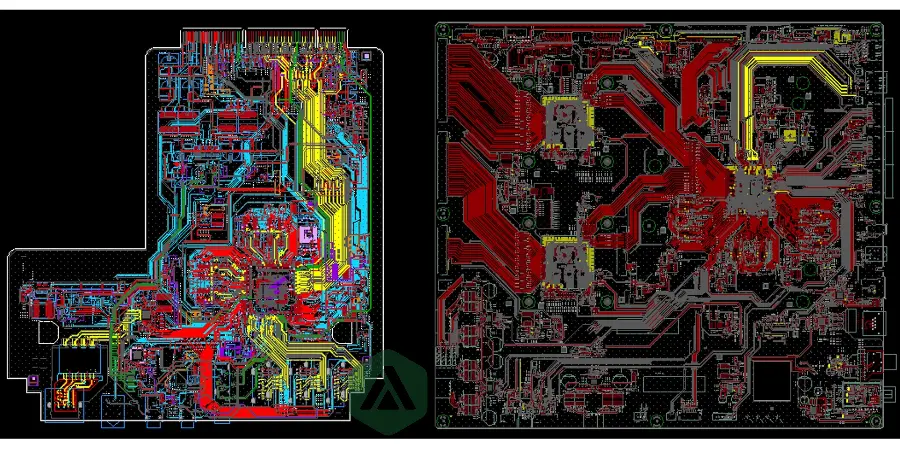

An smt stencil design tutorial covers more than just cutting holes in metal. It defines the interaction between the PCB pad, the solder paste rheology, and the squeegee mechanics. The scope of stencil design includes the selection of the mounting method (framed vs. frameless), the manufacturing technology (laser-cut vs. electroformed), and the specific aperture modifications required for difficult components like Quad Flat No-leads (QFNs) or Ball Grid Arrays (BGAs).

The boundaries of this process are defined by the manufacturing capabilities. For instance, a standard laser cutter has a beam diameter of roughly 20µm to 40µm. This physical limit dictates the minimum corner radius of an aperture. If a design requires sharper corners than the laser can cut, the paste release will suffer. Furthermore, the design must account for downstream processes. If the board requires mixed assembly, the stencil design must align with the selective solder design or wave solder fixture guide to ensure no paste interferes with subsequent masking or tooling.

Correct design ensures "Transfer Efficiency"—the percentage of paste volume that actually transfers from the aperture to the pad. A theoretical volume of 100% is rarely achieved; a well-designed process targets 80% to 110% volume transfer. Anything below 70% typically results in insufficient solder joints (opens), while anything above 120% risks short circuits (bridging).

Metrics That Matter (How to Evaluate It)

To ensure high-yield production, engineers must evaluate specific geometric and process metrics. These numbers determine whether a stencil will physically work or fail immediately on the line.

Geometry and Design Limits

The following table outlines the hard limits for stencil geometry. Violating these usually requires a change in foil thickness or aperture size.

| Metric | Standard Limit | High-Reliability Limit | Why It Matters | How to Verify |

|---|---|---|---|---|

| Area Ratio (AR) | $\ge 0.66$ | $\ge 0.70$ | Determines if paste releases from the aperture. | Calculate: $Area / (Perimeter \times Thickness)$. |

| Aspect Ratio | $\ge 1.5$ | $\ge 1.6$ | Prevents paste from clogging inside the aperture. | Calculate: $Aperture Width / Foil Thickness$. |

| Wall Roughness | $< 5 \mu m$ | $< 3 \mu m$ | Rough walls hold paste, reducing transfer efficiency. | Microscope inspection or profilometer. |

| Positional Accuracy | $\pm 15 \mu m$ | $\pm 10 \mu m$ | Ensures aperture aligns exactly with the PCB pad. | CMM (Coordinate Measuring Machine) scan. |

| Foil Tension | $> 35 N/cm$ | $> 40 N/cm$ | Prevents "coining" or smearing during separation. | Tension gauge measurement at 5 points. |

| Fiducial Contrast | High | High | Machine vision must recognize alignment marks instantly. | Visual check; verify half-etch darkness. |

Process and Performance Metrics

Once the stencil is in the machine, these metrics define success.

| Metric | Acceptable Range | Critical Threshold | Why It Matters | How to Verify |

|---|---|---|---|---|

| Transfer Efficiency | 80% – 120% | $< 70%$ | Low efficiency causes open joints; high causes shorts. | SPI Inspection (Volume measurement). |

| Wipe Frequency | Every 3–5 prints | Every 1 print | Frequent cleaning slows throughput and indicates poor release. | Monitor cycle time and print defects. |

| Paste Height | Foil Thickness $\pm 15%$ | $\pm 25%$ | Consistent height proves consistent pressure and release. | SPI Height Map. |

| Bridge Width | $\ge 150 \mu m$ | $< 100 \mu m$ | Thin steel webs between apertures break easily. | Design Rule Check (DRC) on Gerber. |

How to Choose (Selection Guidance by Scenario)

Selecting the right stencil parameters is a series of "if-then" decisions based on component density and PCB technology. Use these 10 rules to guide your configuration.

- If the smallest component pitch is < 0.5mm (e.g., fine-pitch BGA or QFN), choose a foil thickness of 100µm (4 mil) or 120µm (5 mil) to maintain proper Area Ratios.

- If the design contains standard 1206/0805 passives and 1.27mm pitch ICs, choose a standard 127µm (5 mil) or 150µm (6 mil) foil for robust solder joints.

- If the PCB has a mix of large connectors (requiring high volume) and fine-pitch BGAs (requiring low volume), choose a Step-Stencil (step-down for fine pitch or step-up for connectors).

- If the component is a QFN with a large center ground pad, choose a Window Pane aperture design with 50% to 80% area coverage to prevent component floating and voiding.

- If you are running a high-volume production (> 50,000 cycles), choose a Nanocoating treatment to improve paste release and reduce under-stencil cleaning frequency.

- If the aperture width is less than 0.25mm, choose Electropolishing post-processing to smooth the aperture walls and improve transfer efficiency.

- If you are prototyping and need to minimize cost, choose a Frameless (Foil-only) system compatible with a universal tensioning frame (e.g., VectorGuard).

- If the board uses 0201 or 01005 passives, choose Home Plate or Inverted Home Plate aperture shapes to reduce solder balling at the component flanks.

- If the PCB requires subsequent wave soldering, choose aperture reductions that keep paste away from through-holes to ensure compatibility with the wave solder fixture guide.

- If the stencil life must exceed 100,000 prints, choose SUS304-H (High Tension) stainless steel rather than standard tension steel to maintain registration accuracy over time.

Implementation Checkpoints (Design to Manufacturing)

Follow this 10-step workflow to move from a PCB layout to a production-ready stencil. Each step includes a specific acceptance check.

Export Paste Layer (Gerber/ODB++)

- Action: Generate the paste mask layer from the ECAD software. Ensure it is 1:1 with the copper pads initially.

- Acceptance Check: Verify the file extension and that no non-paste features (like board outlines) are on the paste layer.

Apply Global Reduction

- Action: Apply a global reduction of 10% to 15% by area or 0.05mm per side. This compensates for paste spread during reflow.

- Acceptance Check: Measure a standard 0603 pad; the aperture should be smaller than the copper pad.

Calculate Area Ratios (AR)

- Action: Run a script or manual check on the smallest apertures against the chosen foil thickness.

- Acceptance Check: All AR values must be ≥ 0.66. If not, reduce foil thickness or enlarge aperture (if spacing permits).

Optimize QFN/Thermal Pads

- Action: Segment large thermal pads into a grid (window pane). Web width between panes should be ≥ 0.2mm.

- Acceptance Check: Total paste coverage on the thermal pad is between 50% and 80%.

Adjust for Fine Pitch (BGA/0201)

- Action: Change aperture shape for BGAs to "squircle" (square with rounded corners) or circles. Apply specific reductions for 0201s to prevent tombstoning.

- Acceptance Check: BGA aperture diameter is ≤ pad diameter.

Place Fiducial Marks

- Action: Add half-etched or cut-through fiducials. These must match the PCB fiducial locations exactly.

- Acceptance Check: At least 3 fiducials are present (2 global, 1 local for fine pitch) and clearly defined.

Select Foil Thickness and Material

- Action: Finalize thickness (e.g., 127µm) based on the AR check. Specify stainless steel grade.

- Acceptance Check: Selected thickness is listed in the fabrication drawing.

Define Frame and Text

- Action: Choose frame size (e.g., 29" x 29") and add identification text (Part Number, Thickness, Date) to the stencil border.

- Acceptance Check: Text is on the squeegee side (readable) and does not interfere with the print area.

Manufacturing (Laser Cut & Post-Process)

- Action: Send to PCB Stencil manufacturer. Request electropolish if needed.

- Acceptance Check: Manufacturer confirms data integrity and capability to cut specified tolerances.

Incoming Quality Control (IQC)

- Action: Upon receipt, measure tension and inspect critical apertures.

- Acceptance Check: Tension > 35 N/cm; Aperture sizes match Gerber within ± 9µm.

Common Mistakes (and the Correct Approach)

Even experienced engineers fall into these traps. Here is how to identify and fix them.

Mistake: 1:1 Aperture Scaling

- Impact: Excessive solder paste leads to bridging (shorts) and solder balls, especially on fine-pitch ICs.

- Fix: Apply a global reduction of 10-20% by area.

- Verify: Check that the aperture is visibly smaller than the copper pad in the CAM viewer.

Mistake: Ignoring Aspect Ratio on 0201s

- Impact: Paste clogs the aperture and does not release, causing open joints.

- Fix: Reduce foil thickness to 100µm or increase aperture size slightly if spacing allows.

- Verify: Calculate AR; ensure it is > 0.66.

Mistake: Over-reduction on Lead-Free Paste

- Impact: Lead-free alloys (SAC305) do not wet/spread as well as SnPb. Over-reduction leads to exposed copper edges.

- Fix: Use a conservative reduction (1:1 or 5% reduction) for lead-free processes on large pads.

- Verify: Inspect reflowed joints for full pad coverage.

Mistake: Missing Relief for Solder Mask

- Impact: If the stencil sits on top of thick solder mask or nomenclature (silkscreen), it creates a "gasket" gap, causing paste smearing.

- Fix: Ensure the stencil area is clear of raised markings, or use a step-relief (etched pocket) on the PCB side of the stencil.

- Verify: Check PCB topography against stencil layout.

Mistake: Wrong Step-Stencil Configuration

- Impact: The squeegee blade gets damaged or prints unevenly if the "step" is too steep or close to apertures.

- Fix: Maintain a keep-out distance of 3mm to 5mm around the step edge.

- Verify: Measure distance from step edge to nearest aperture.

Mistake: Neglecting Glue Stencils

- Impact: For double-sided reflow or wave soldering, components must be glued. Using a paste stencil design for glue results in insufficient adhesion.

- Fix: Use specific glue aperture designs (often keyhole or double-dot) with greater height.

- Verify: Shear test the glued components before soldering.

Mistake: Inverted Layers

- Impact: The stencil is cut as a mirror image.

- Fix: Clearly label

Glossary (Key Terms)

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: layout rules that reduce defects. | Prevents rework, delays, and hidden cost. |

| AOI | Automated Optical Inspection used to find solder/assembly defects. | Improves coverage and catches early escapes. |

| ICT | In-Circuit Test that probes nets to verify opens/shorts/values. | Fast structural test for volume builds. |

| FCT | Functional Circuit Test that powers the board and checks behavior. | Validates real function under load. |

| Flying Probe | Fixtureless electrical test using moving probes on pads. | Good for prototypes and low/medium volume. |

| Netlist | Connectivity definition used to compare design vs manufactured PCB. | Catches opens/shorts before assembly. |

| Stackup | Layer build with cores/prepreg, copper weights, and thickness. | Drives impedance, warpage, and reliability. |

| Impedance | Controlled trace behavior for high-speed/RF signals (e.g., 50Ω). | Avoids reflections and signal integrity failures. |

| ENIG | Electroless Nickel Immersion Gold surface finish. | Balances solderability and flatness; watch nickel thickness. |

| OSP | Organic Solderability Preservative surface finish. | Low cost; sensitive to handling and multiple reflows. |

SMT Stencil Design Tutorial FAQ

What Is smt stencil design tutorial (in One Sentence)?

It’s a practical set of requirements and checks that defines how you will build, verify, and accept the product.

- Clarify scope and boundaries.

- Define pass/fail criteria.

- Align DFM + test coverage.

How Much Does smt stencil design tutorial Typically Cost?

Cost depends on layer count, materials, finish, test method, and engineering review effort.

- Provide quantities and stackup early.

- Call out impedance, via-in-pad, microvias.

- Ask for DFM notes before quoting.

What Drives Lead Time for smt stencil design tutorial?

Lead time is driven by data completeness, material availability, and test/inspection requirements.

- Avoid missing drill/stackup.

- Confirm material substitutions.

- Lock panelization early.

What Files Should I Send for smt stencil design tutorial?

Send Gerbers/ODB++, NC drill, stackup notes, fab drawing, and test requirements.

- Include version + date.

- Provide impedance targets and tolerances.

- Attach BOM if PCBA.

How Do I Define Acceptance Criteria for smt stencil design tutorial?

Use measurable criteria tied to IPC class, electrical test coverage, and functional validation.

- State IPC class.

- Specify E-test/netlist.

- List functional test cases.

Which Surface Finish Is Best for smt stencil design tutorial?

Choose based on pitch/flatness needs, cost targets, and reliability requirements.

- ENIG for fine pitch/BGA.

- OSP for low-cost builds.

- Avoid HASL for very fine pitch.

How Many Test Points Do I Need for smt stencil design tutorial?

Enough to support the test strategy (flying probe/ICT/FCT) with margin.

- Plan early in layout.

- Keep access away from tall parts.

- Document probe pad size.

What Are the Most Common Failures in smt stencil design tutorial?

Data issues, insufficient test coverage, and uncontrolled process limits are the most common causes.

- Watch annular ring/registration.

- Control solder mask openings.

- Verify impedance and warpage.

Conclusion

smt stencil design tutorial is easiest to get right when you define the specifications and verification plan early, then confirm them through DFM and test coverage.

Use the rules, checkpoints, and troubleshooting patterns above to reduce iteration loops and protect yield as volumes increase.

If you’re unsure about a constraint, validate it with a small pilot build before locking the production release.