Key Takeaways

- Definition Scope: Three-phase inverter control PCB layout involves the physical arrangement of gate drivers, microcontrollers, and sensing circuits while maintaining strict isolation from high-voltage power stages.

- Critical Metric: Loop inductance in the gate drive path is the single most important factor affecting switching efficiency and electromagnetic interference (EMI).

- Isolation is Key: Proper creepage and clearance distances between the high-voltage side (DC link/IGBTs) and the low-voltage side (MCU/DSP) are non-negotiable for safety.

- Thermal Management: Even control boards require thermal strategies, particularly for gate driver ICs driving large capacitive loads.

- Validation: Simulation is not enough; double-pulse testing and thermal imaging are required to validate the layout physically.

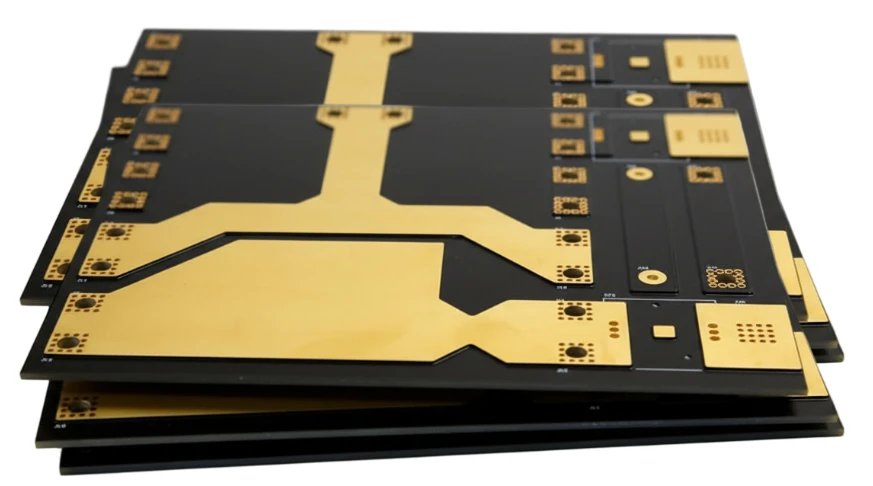

- Manufacturing Readiness: Design for Manufacturing (DFM) must address heavy copper requirements and layer stackup symmetry to prevent warpage.

What “three-phase inverter control PCB” means (scope & boundaries)

The term Three-phase inverter control PCB layout refers to the specific engineering discipline of designing the printed circuit board that manages the switching of a three-phase power inverter. While the "power stage" handles the raw current (often hundreds of Amps), the "control layout" is the brain and nervous system. It translates digital logic (PWM signals) into physical gate drive voltages while reading analog feedback (current, voltage, temperature).

This layout task is unique because it sits at the intersection of sensitive digital signals and violent high-voltage switching events. A poor layout does not just mean a non-functional board; it often results in catastrophic failure of power modules due to false triggering or voltage spikes.

At APTPCB (APTPCB PCB Factory), we often see designs that function perfectly in simulation but fail in the real world due to parasitic inductance hidden in the PCB layout. The scope of this guide covers the layout from the microcontroller (MCU) output, through the isolation barrier, to the gate driver, and finally to the interface with the power switches (IGBTs, MOSFETs, or SiC/GaN devices).

Metrics that matter (how to evaluate quality)

To determine if a Three-phase inverter control PCB layout is robust, you must measure specific physical and electrical parameters. These metrics define the difference between a prototype and a production-ready board.

| Metric | Why it matters | Typical range or influencing factors | How to measure |

|---|---|---|---|

| Gate Loop Inductance | High inductance causes ringing, voltage overshoot, and slower switching speeds. | Target: < 10 nH. Influenced by trace length and return path proximity. | Q3D Extractor simulation or V_ds overshoot observation. |

| Common Mode Transient Immunity (CMTI) | Determines if the isolator can withstand rapid voltage changes (dV/dt) without data corruption. | > 50 kV/µs for Si; > 100 kV/µs for SiC/GaN. | Pulse generator tests across the isolation barrier. |

| Creepage Distance | Prevents electrical tracking across the PCB surface under pollution and humidity. | Dependent on voltage (e.g., 8mm for 400V systems under pollution degree 2). | Physical measurement (calipers) or CAD rule checks. |

| Clearance Distance | Prevents air breakdown (arcing) between high and low voltage nets. | Defined by IPC-2221 or IEC 60664-1 standards. | CAD Design Rule Check (DRC). |

| Thermal Resistance (Rth) | Ensures gate drivers and regulators do not overheat during high-frequency switching. | Dependent on copper thickness and thermal vias. | Thermal camera imaging under load. |

| Signal-to-Noise Ratio (SNR) | Critical for current sensing feedback (ADC lines). Noise leads to torque ripple in motors. | Target: > 60 dB. Influenced by ground plane separation. | Oscilloscope analysis of analog feedback lines. |

Design choices by scenario (trade-offs)

Different applications require drastically different approaches to Three-phase inverter control PCB design. Below are common scenarios and the necessary trade-offs.

1. Low-Voltage Motor Drives (12V - 48V)

- Context: Battery-powered tools, e-bikes, robotics.

- Trade-off: Space is the primary constraint.

- Guidance: You can often combine power and control on a single PCB. Use Heavy Copper PCB technology to handle the current in a small footprint. Isolation requirements are less stringent, allowing tighter component placement.

2. Industrial AC Drives (400V - 690V)

- Context: Factory automation, pumps, fans.

- Trade-off: Reliability and safety are paramount over size.

- Guidance: Strict adherence to IEC 61800-5-1. Use a dedicated control board separated from the power stage, connected via headers or press-fit pins. Prioritize wide creepage slots.

3. EV Traction Inverters (High Power Density)

- Context: Electric vehicle main drive.

- Trade-off: High vibration and extreme thermal cycling.

- Guidance: Use automotive-grade materials. The layout must support high dV/dt (especially with SiC). Often requires High Thermal PCB substrates or metal-core designs for the driver stage to dissipate heat into the cooling system.

4. Solar Inverters (Grid-Tied)

- Context: PV energy conversion.

- Trade-off: Efficiency and longevity (20+ year lifespan).

- Guidance: Minimize losses in the gate drive to improve total system efficiency. Layout must account for high DC bus voltages (up to 1500V), requiring significant isolation barriers and possibly conformal coating.

5. High-Frequency GaN/SiC Drivers

- Context: Server power supplies, compact chargers.

- Trade-off: Extremely fast switching speeds vs. EMI.

- Guidance: Loop inductance must be near zero. The driver must be placed physically as close as possible to the switch. Often requires HDI (High Density Interconnect) techniques to place drivers directly under or over the switches.

6. Cost-Sensitive Consumer Appliances

- Context: Washing machines, HVAC units.

- Trade-off: Cost vs. Performance.

- Guidance: Single-layer or two-layer boards are common to save cost. This makes routing the return paths difficult. Designers must use "star ground" techniques meticulously to prevent noise coupling without the luxury of full ground planes.

Implementation checkpoints (design to manufacturing)

Moving from a schematic to a physical board requires a disciplined process. Use this checklist to ensure your Three-phase inverter control PCB layout is ready for production at APTPCB.

Stackup Definition:

- Recommendation: Use a 4-layer minimum for industrial inverters (Signal-Ground-Power-Signal).

- Risk: 2-layer boards often fail EMI testing due to broken return paths.

- Acceptance: Verify impedance profiles and layer symmetry.

Placement of Gate Drivers:

- Recommendation: Place drivers within 10mm of the power module pins or MOSFET gates.

- Risk: Long traces act as antennas and add inductance.

- Acceptance: Visual inspection of distance.

Kelvin Connection for Current Sensing:

- Recommendation: Route differential pairs for current sense resistors tightly together.

- Risk: Picking up switching noise in the feedback loop causes control instability.

- Acceptance: Verify differential routing in CAD.

Isolation Barrier Width:

- Recommendation: Physically mill a slot (air gap) under optocouplers or digital isolators if voltage exceeds 400V.

- Risk: PCB carbonization over time leading to shorts.

- Acceptance: Check Gerber files for milling layer data.

Desaturation Protection Routing:

- Recommendation: Keep the DESAT detection trace short and away from high dV/dt nodes.

- Risk: False tripping of short-circuit protection.

- Acceptance: Review noise coupling on the DESAT pin during simulation.

Ground Plane Separation:

- Recommendation: Distinctly separate AGND (Analog), DGND (Digital), and PGND (Power) and join them at a single point (Net Tie).

- Risk: Ground loops injecting power noise into the MCU.

- Acceptance: Highlight ground nets in CAD to verify separation.

Power Supply Decoupling:

- Recommendation: Place low-ESR capacitors immediately at the power pins of the gate driver.

- Risk: Voltage droop during the gate charging current spike.

- Acceptance: Verify capacitor placement is on the same layer as the IC where possible.

DFM Review:

- Recommendation: Submit data for a DFM Guideline check before ordering.

- Risk: Unmanufacturable drill hits or acid traps.

- Acceptance: Supplier approval report.

Common mistakes (and the correct approach)

Even experienced engineers make errors in Three-phase inverter control PCB design. Here are the most frequent issues we encounter.

- Mistake: Routing Gate Drive traces through vias.

- Correction: Vias add inductance (approx. 1.2nH per via). Keep the high-current gate charge/discharge path on the top layer without layer changes if possible.

- Mistake: Ignoring the "Miller Clamp" path.

- Correction: The path that prevents false turn-on (Miller effect) is just as critical as the turn-on path. Keep it short and wide.

- Mistake: Placing the temperature sensor far from the hot spot.

- Correction: NTC/PTC sensors must be thermally coupled to the IGBT/MOSFET case or the hottest part of the PCB, not just "nearby."

- Mistake: Overlooking Copper Balance.

- Correction: Large copper pours on one side and sparse traces on the other cause warping during reflow. Use copper thieving (hatching) to balance the layers.

- Mistake: Running sensitive signals under the power module.

- Correction: Never route ADC or communication lines on layers directly beneath the switching power semiconductors. The capacitive coupling will inject noise.

- Mistake: Inadequate Silk Screen markings.

- Correction: Clearly mark High Voltage areas. This is a safety requirement for assembly and testing personnel.

FAQ

Q: How many layers are best for a Three-phase inverter control PCB? A: For simple low-voltage drives, 2 layers may suffice. For 400V+ industrial drives, 4 layers are standard to provide solid ground planes. Complex EV inverters often use 6 or more layers.

Q: Should I use a ground plane under the isolation transformer/coupler? A: Absolutely not. You must remove all copper on all layers underneath the isolation barrier components to maintain creepage and clearance.

Q: What copper weight should I specify? A: For the control signals, standard 1oz (35µm) is fine. However, if the board also carries the main power current, you might need Industrial Control PCB standards, which often utilize 2oz or 3oz copper.

Q: How do I reduce EMI in the layout? A: Minimize the loop area of the high di/dt paths (gate drive loops and DC link loops). Use a solid ground plane for the control logic. Slow down switching edges (gate resistors) if efficiency targets allow.

Q: Can I use FR4 material for high-voltage inverters? A: Yes, standard FR4 is suitable for most industrial inverters up to 1000V, provided the layout respects creepage rules. For very high temperatures (>130°C continuous), high-Tg FR4 is recommended.

Q: What is the best way to test the layout before full power? A: Use the "Double Pulse Test" at lower voltages first. This allows you to check switching characteristics and gate drive ringing without risking the full power stage.

Related pages & tools

- Heavy Copper PCB: Essential for inverters where the control board also handles significant power distribution.

- Industrial Control PCB: Specific capabilities for rugged, high-reliability industrial drive electronics.

- DFM Guidelines: Check your layout against manufacturing constraints before submission.

- Power & Energy PCB: Solutions tailored for solar, wind, and grid-tie inverter applications.

Glossary (key terms)

| Term | Definition |

|---|---|

| DC Link | The DC voltage source (capacitor bank) that feeds the inverter. |

| IGBT | Insulated Gate Bipolar Transistor. A common power switch for high-voltage inverters. |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor. Used for lower voltage or higher frequency inverters. |

| Gate Driver | An IC that amplifies low-power logic signals to high-current pulses to drive IGBT/MOSFET gates. |

| Dead Time | A short pause between switching off one transistor and turning on the other in the same leg to prevent short circuits. |

| PWM | Pulse Width Modulation. The method used to encode analog signal levels into digital pulses. |

| dV/dt | The rate of change of voltage. High dV/dt can cause noise coupling across isolation barriers. |

| dI/dt | The rate of change of current. High dI/dt induces voltage spikes across stray inductances. |

| Kelvin Connection | A 4-wire connection method used to measure voltage across a component (like a shunt) without including the voltage drop of the carrying wires. |

| Creepage | The shortest distance between two conductive parts along the surface of the insulation. |

| Clearance | The shortest distance between two conductive parts through the air. |

| EMI | Electromagnetic Interference. Noise generated by switching that affects other electronics. |

| EMC | Electromagnetic Compatibility. The ability of the device to operate without causing or suffering from EMI. |

Conclusion (next steps)

Mastering Three-phase inverter control PCB layout is a balance of electrical theory, safety standards, and physical manufacturing constraints. A successful layout protects the sensitive digital brain from the high-power brawn, ensuring efficiency and reliability.

When you are ready to move from design to prototype, APTPCB is here to assist. To get an accurate quote and a comprehensive DFM review, please provide:

- Gerber Files (RS-274X format).

- Stackup details (Copper weight, dielectric thickness).

- Material specifications (Tg rating, CTI value for high voltage).

- Special requirements (Milling for isolation slots, heavy copper, or specific solder mask colors for contrast).

Ensuring these details are clear will speed up the manufacturing process and help us deliver a board that meets the rigorous demands of power electronics.