Key Takeaways

- Definition: A Time Base Corrector (TBC) is a circuit or device that corrects timing instabilities (jitter) in electronic signals, ensuring synchronization between source and display or processing units.

- Core Function: It utilizes buffers (FIFO) and stable clock references to realign signal data, crucial for both legacy video and modern high-speed data transmission.

- Critical Metrics: Success depends on measuring Jitter Attenuation, Lock Range, and Insertion Delay.

- PCB Layout: Proper impedance control and ground plane integrity are non-negotiable for TBC circuits to function without introducing new noise.

- Misconception: TBCs are not just for old VCRs; they are essential in modern FPGA-based video processing and complex

Active Speaker PCBdesigns for audio sync. - Validation: Functional testing must verify that the output signal remains stable even when the input signal degrades or drifts.

What Time Base Corrector really means (scope & boundaries)

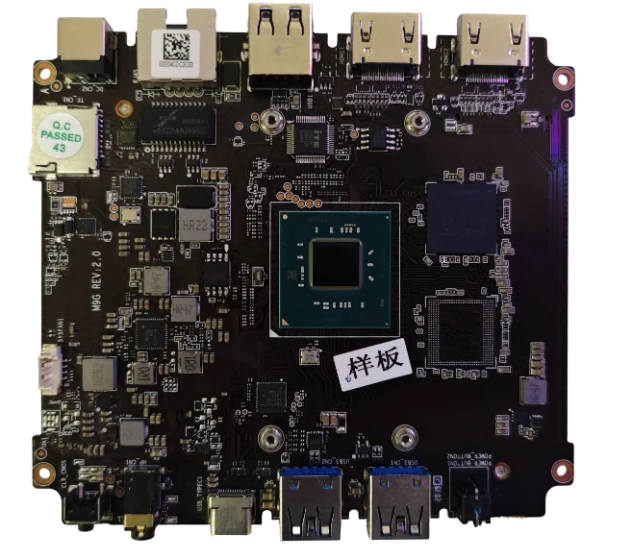

While the key takeaways highlight the basic function, understanding the full scope of a Time Base Corrector requires looking beyond simple definitions. In the context of electronics manufacturing at APTPCB (APTPCB PCB Factory), a TBC is not merely a standalone box for vintage tapes but a critical subsystem within complex circuit boards.

Fundamentally, a TBC addresses the problem of "time base errors." In analog video, this manifests as wavy lines or skew. In digital systems, it appears as jitter or clock domain crossing errors. The TBC writes the incoming signal into a memory buffer using the unstable clock derived from the source. It then reads that data out using a highly stable, locally generated crystal clock. This process effectively "cleans" the signal timing.

Modern applications extend to Color Corrector PCB designs, where precise timing is required to align chroma and luma signals before color grading processing. If the timing is off by even nanoseconds, color artifacts appear. Therefore, when we discuss TBCs in this guide, we cover the entire chain: the input conditioning, the memory buffer (FIFO), the clock generation (PLL), and the output drivers.

Metrics that matter (how to evaluate quality)

Once you understand the scope of the device, you must quantify its performance using specific engineering metrics. A TBC is only as good as its ability to reject instability without degrading the signal.

| Metric | Why it matters | Typical Range / Factors | How to Measure |

|---|---|---|---|

| Jitter Attenuation | Determines how much input timing noise is removed. | -20dB to -60dB depending on PLL bandwidth. | Spectrum Analyzer or Jitter Meter. |

| Lock Range | The frequency range over which the TBC can synchronize with the input. | ±100 ppm to ±5% of center frequency. | Sweep input frequency until lock is lost. |

| Insertion Delay | The time it takes for the signal to pass through the buffer. | 1 line (video) to several frames; nanoseconds for data. | Oscilloscope (Input vs. Output delta). |

| Residual Time Base Error (TBE) | The remaining timing error after correction. | < 2ns for broadcast video; < 10ps for high-speed data. | Vector Scope or Time Interval Analyzer. |

| Signal-to-Noise Ratio (SNR) | Ensures the correction process doesn't add electronic noise. | > 60dB for video; > 100dB for high-end audio. | Audio/Video Analyzer. |

| Sampling Rate | Defines the resolution of the digital correction. | 4x Subcarrier (video) or Nyquist compliant (data). | Verify against system clock specs. |

Selection guidance by scenario (trade-offs)

Metrics provide the data, but the correct Time Base Corrector choice depends entirely on the specific operational scenario. Different industries prioritize different trade-offs between latency, cost, and precision.

1. Legacy Video Restoration (Analog)

- Goal: Stabilize VHS/Betamax signals for digitization.

- Priority: High tolerance for bad sync pulses (dropout compensation).

- Trade-off: Higher latency is acceptable (frame-level buffering).

- Hardware: Dedicated DSP or FPGA with large SDRAM buffers.

2. Broadcast Video Processing (SDI/HDMI)

- Goal: Synchronize multiple camera feeds (Genlock).

- Priority: Extremely low jitter and strict standard compliance.

- Trade-off: High cost; requires complex High Speed PCB design techniques.

- Hardware: FPGA with internal SerDes and external VCXO.

3. High-Fidelity Audio Systems

- Goal: Eliminate phase drift between channels in an

Active Speaker PCB. - Priority: Phase coherence and low noise floor.

- Trade-off: Throughput speed is less critical than timing precision.

- Hardware: Audio-specific PLLs and FIFO re-clockers.

4. Security and Surveillance (Long Cable Runs)

- Goal: Correct signal degradation over long coaxial cables.

- Priority: Robustness against attenuation and ground loops.

- Trade-off: Lower resolution support is often acceptable.

- Hardware: Integrated analog front-end (AFE) chips with built-in TBC.

5. Color Correction Suites

- Goal: Pixel-perfect alignment for a

Color Corrector PCB. - Priority: Linearity and chroma bandwidth.

- Trade-off: Power consumption is high due to processing load.

- Hardware: High-end ASIC or FPGA solutions.

6. Industrial Data Acquisition

- Goal: Synchronize sensors across different clock domains.

- Priority: Deterministic latency.

- Trade-off: Buffer size is kept small to minimize delay.

- Hardware: Dual-port RAM or specialized FIFO buffers.

From design to manufacturing (implementation checkpoints)

After selecting the right architecture, the focus shifts to physical implementation where manufacturing realities meet design theory. At APTPCB, we see that most TBC failures stem from layout oversight rather than component failure.

| Checkpoint | Recommendation | Risk | Acceptance Method |

|---|---|---|---|

| Stackup Design | Use a symmetrical stackup with dedicated ground planes adjacent to signal layers. | Impedance mismatch causes reflections, increasing jitter. | Impedance Calculator verification. |

| Clock Routing | Route clock signals first; use differential pairs where possible. | Crosstalk can corrupt the reference clock, rendering the TBC useless. | Simulation (Signal Integrity) & Eye Diagram. |

| Power Integrity | Place decoupling capacitors (0.1µF, 10µF) close to TBC IC power pins. | Voltage ripples induce phase noise in the PLL. | Power Integrity (PI) Simulation. |

| Crystal Placement | Isolate the crystal oscillator from heat sources and high-current traces. | Thermal drift alters the frequency stability. | Thermal profiling during prototyping. |

| Return Paths | Ensure solid ground reference under all high-speed traces. | Ground loops introduce hum and timing errors. | Gerber review for split planes. |

| Component Tolerance | Use 1% or better resistors/capacitors in the PLL loop filter. | Loop instability or inability to lock. | BOM validation. |

| Thermal Management | Use thermal vias for the main FPGA/DSP processor. | Overheating leads to data corruption or shutdown. | Thermal camera inspection. |

| Connector Quality | Use 75-ohm (video) or 50-ohm (data) rated connectors. | Signal loss at the interface point. | TDR (Time Domain Reflectometry) test. |

Common mistakes (and the correct approach)

Even with a checklist, engineers often fall into specific traps when integrating a Time Base Corrector. Avoiding these pitfalls saves revision cycles.

Ignoring the "Clean" Clock Source:

- Mistake: Using a noisy switching power supply to power the crystal oscillator.

- Correction: Use a dedicated LDO (Low Dropout Regulator) for the clock generation circuit to minimize phase noise.

Oversizing the Buffer:

- Mistake: Using a massive frame buffer when only a few lines are needed.

- Correction: Calculate the maximum expected jitter frequency. If the drift is slow, you need a larger buffer. If it is high-frequency jitter, a smaller, faster buffer is superior and reduces latency.

Neglecting Thermal Drift:

- Mistake: Placing the TBC circuit near power MOSFETs on an

Active Speaker PCB. - Correction: Physical isolation is key. Heat changes the propagation delay of traces and the frequency of crystals.

- Mistake: Placing the TBC circuit near power MOSFETs on an

Poor Grounding Strategy:

- Mistake: Mixing analog and digital grounds improperly under the TBC chip.

- Correction: Use a unified ground plane for high-speed digital TBCs, or carefully bridge analog/digital grounds at a single point (star ground) if using mixed-signal ICs.

Overlooking Cable Equalization:

- Mistake: Assuming the TBC fixes amplitude loss.

- Correction: A TBC fixes timing. You must add an equalizer (EQ) stage before the TBC if the input signal amplitude is attenuated.

Software-Only Reliance:

- Mistake: Attempting to fix severe hardware jitter purely in software post-processing.

- Correction: Hardware TBCs are required for real-time capture. Software cannot recover data that was lost due to sync failure at the A/D converter.

FAQ

To wrap up the technical details, here are answers to the most frequent questions we receive regarding TBC implementation.

Q: Can a Time Base Corrector improve image resolution? A: No. A TBC stabilizes the signal timing and geometry. It does not add pixels or increase resolution, though a stable image often looks sharper.

Q: What is the difference between a Line TBC and a Full Frame TBC? A: A Line TBC corrects jitter within individual scan lines (horizontal sync). A Full Frame TBC stores the entire image, correcting vertical sync and frame rate issues, but introduces more latency.

Q: Do I need a TBC for HDMI signals? A: HDMI uses digital packet transmission. While "jitter cleaning" is used in HDMI re-drivers, the term "Time Base Corrector" usually applies to analog or raw stream processing. However, the underlying PLL principles are identical.

Q: How does a TBC affect audio in video streams? A: If a Frame TBC delays video to correct it, the audio must be delayed by the same amount. Failure to do this results in lip-sync errors.

Q: Why is impedance control critical for TBC PCBs? A: TBCs operate at high frequencies. Mismatched impedance causes signal reflections, which look like "ghosts" or noise to the TBC, making it harder to lock onto the sync pulse.

Q: Can APTPCB manufacture boards with embedded TBC circuits? A: Yes. We specialize in Testing and Quality assurance for high-precision boards, including those with sensitive clock domains and FPGA-based TBCs.

Q: What is the cost impact of adding a TBC? A: It adds cost due to the need for memory chips (RAM), an FPGA or specialized IC, and a high-quality crystal oscillator. It also requires a multilayer PCB stackup.

Q: Is a TBC necessary for an Active Speaker PCB? A: For standalone speakers, no. For wireless or networked active speakers, a mechanism similar to a TBC (clock recovery) is essential to keep left/right channels perfectly synchronized.

Glossary (key terms)

Understanding the specific vocabulary is essential for communicating with design teams and manufacturers.

| Term | Definition |

|---|---|

| Jitter | The deviation of a signal pulse from its ideal timing position. |

| PLL (Phase Locked Loop) | A control system that generates an output signal whose phase is related to the phase of an input signal. |

| Genlock | Generator Locking; a technique to synchronize the video sources of one or more cameras. |

| Chroma | The color information in a video signal. |

| Luma | The brightness information in a video signal. |

| FIFO (First-In, First-Out) | A memory buffer method used to store data temporarily for timing correction. |

| Burst Signal | A reference signal used to synchronize the color oscillator in video. |

| V-Sync / H-Sync | Vertical and Horizontal synchronization pulses that define the frame and line boundaries. |

| Dropout | A momentary loss of signal, often caused by physical defects in magnetic tape. |

| Artifact | Visual anomalies introduced during signal processing or compression. |

| Skew | A distortion where the top of the image bends to the left or right. |

| Clock Domain | A section of a logic design driven by a single clock signal. |

Conclusion (next steps)

A Time Base Corrector is a sophisticated subsystem that demands rigorous attention to signal integrity, power stability, and thermal management. Whether you are designing a vintage restoration tool, a modern Color Corrector PCB, or a synchronized Active Speaker PCB, the principles of buffering and re-clocking remain constant. The difference between a functional prototype and a production-ready device often lies in the quality of the PCB layout and the precision of the manufacturing process.

If you are ready to move your design from concept to reality, ensure your data package is complete. For a seamless DFM review and accurate quote, please provide your Gerber files, stackup requirements, and specific impedance constraints. APTPCB is equipped to handle the complexities of high-speed, low-jitter circuitry.

Contact us today to discuss your project requirements or upload your files for an immediate review.