The simulation says 50Ω. The hardware says something else. This gap—between the EM model and the physical board—is the most common and most expensive problem in Rogers circuit board design. It has specific, identifiable causes, and most of them can be eliminated before Gerbers are generated.

This guide is structured as a practical engineering walkthrough: from stackup definition through trace geometry, via transition modeling, thermal design, and the DFM checkpoints that determine whether manufactured hardware performs like the simulation. The focus is on design decisions that translate directly into fabrication specifications—not just concepts, but the numbers that go on a drawing. Whether the target application is 5G mmWave, automotive radar, Ka-band satellite terminals, or E-band backhaul, the principles apply across the RO3003 platform.

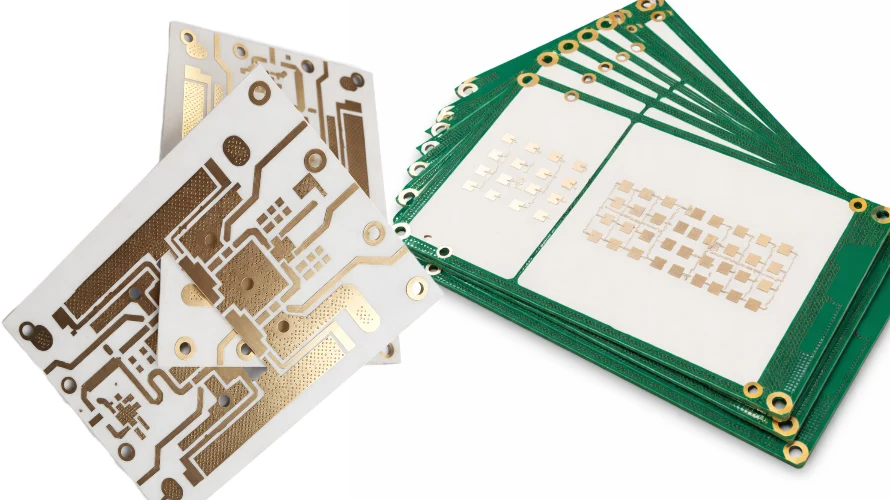

Stackup as the Foundation of RF Design

An EM simulation is only as accurate as the stackup it's built on. The most common mismatch between Rogers circuit board simulations and manufactured hardware comes from designing to nominal Dk and then receiving boards fabricated with a different core thickness or copper weight than what was modeled.

Defining the Stackup Before Simulation

For RO3003 in mmWave applications, the stackup specification requires:

- Core thickness: Nominal and tolerance (Rogers specifies ±10% on standard cores)

- Copper weight: Nominal (0.5 oz, 1 oz, 2 oz) and the finished copper thickness after etching

- Copper foil type: Standard ED or low-profile; the RMS roughness enters the conductor loss calculation directly

- Hybrid construction: If FR-4 inner layers are used, the bonding film thickness and Dk must be included in the model for via transition analysis

The starting point for simulation inputs is the Rogers RO3003 PCB material specification: Dk 3.00 ± 0.04 at 10 GHz, Df 0.0010, TcDk −3 ppm/°C. These values are the datasheet basis; your EM solver should use the measured Dk at your operating frequency (Rogers publishes frequency-dependent permittivity data through their online MWI-2000 impedance calculator).

Core Thickness Tolerance and Impedance Sensitivity

For a 50Ω microstrip on a 10 mil (0.254mm) RO3003 core with 1 oz copper, the nominal trace width is approximately 10 mil. How sensitive is impedance to core thickness variation?

A ±10% core thickness tolerance (±0.025mm on a 10 mil core) produces approximately ±3–4Ω impedance variation at constant trace width. For a ±10% impedance specification (45–55Ω), this is workable. For a tighter ±5% specification (47.5–52.5Ω), the fabricator's measured core thickness must feed into the etch compensation calculation—not the nominal value.

APTPCB measures actual core thickness on incoming Rogers material and uses measured values, not nominal, when computing LDI etch compensation factors for tight-tolerance RF traces. Request this practice explicitly if your impedance specification is tighter than ±10%.

Trace Geometry: The Numbers That Determine RF Performance

50Ω Microstrip Trace Width Calculation

At millimeter-wave frequencies, the skin effect limits current to the outermost ~1.5 μm of the conductor. The surface roughness of the copper foil directly affects RF loss. For the same Dk and trace geometry, low-profile ED copper (Ra ≈ 1.5 μm) produces 20–30% lower conductor loss than standard ED copper (Ra ≈ 5–7 μm). This must be specified in the laminate procurement—not addressed after fabrication.

Approximate 50Ω microstrip trace widths for RO3003 (Dk=3.00, 1 oz copper):

| Core Thickness | ~50Ω Trace Width |

|---|---|

| 5 mil (0.127mm) | ~4–5 mil |

| 10 mil (0.254mm) | ~9–11 mil |

| 20 mil (0.508mm) | ~18–22 mil |

Use the Rogers MWI-2000 calculator or a full-wave EM solver for final trace width values. The IPC-2141A formula gives a starting point; above 30GHz, dispersion effects make full-wave simulation the more reliable basis for high-accuracy designs.

Trace Width Tolerance and Its Effect on Insertion Loss

A ±10% trace width tolerance on a 10 mil trace means the fabricated trace could be 9–11 mil. For microstrip, trace width variation primarily affects impedance rather than conductor loss. The more significant concern is impedance mismatch reflection: a 2Ω impedance error at each end of a transmission line creates a −40 dB return loss floor—typically acceptable, but a 5Ω error from combined trace width and Dk variation can degrade return loss to −26 dB, which is visible in radar and transceiver system noise floors.

For RO3003 programs requiring ±5% impedance tolerance, APTPCB's LDI process achieves this with calibrated etch compensation. Request TDR coupon data showing measured vs. target impedance from a recent production batch before committing to a supplier.

Via Transition Design: The Most Simulated, Most Underbuilt Feature

At millimeter-wave frequencies, a through-hole via connecting a microstrip trace to a buried stripline or to a reference plane is not an ideal short circuit. It's a resonant structure with inductive via barrel, capacitive via pad, and potentially a resonant stub below the last connected layer.

Via Model at High Frequencies

A simplified via equivalent circuit at millimeter-wave frequencies:

- Barrel inductance: ~0.5–1.0 nH for a 0.3mm via in a 10 mil core (increases with via length)

- Pad capacitance: ~0.05–0.1 pF for a standard via pad (excess capacitance, partially compensating barrel inductance)

- Stub resonance: A through-hole via with an unconnected tail below the last connected layer creates a λ/4 resonance. Stub length determines the resonant frequency—in high-frequency RF designs, this stub resonance can fall directly within the operating band and must be eliminated by design

Stub Elimination Methods

Backdrilling: Remove the non-functional portion of the via barrel below the last connected layer using a larger-diameter drill. Back-drill depth accuracy of ±50 μm is required to remove the stub without compromising the adjacent layer connection. APTPCB's CNC back-drilling achieves this tolerance on hybrid RO3003 stackups.

Blind vias: Connect only the outer RO3003 layer to the first inner reference plane without penetrating to lower layers. No stub exists because the via terminates at the target layer. Aspect ratio for blind vias on RO3003 is constrained to 0.8:1 (diameter:depth) to maintain IPC Class 3 plating coverage.

Via pad anti-pad optimization: Reduce the anti-pad (clearance hole in the reference plane beneath the via pad) to tune the via's capacitive loading and partially compensate barrel inductance. This is a simulation-driven adjustment—the optimal anti-pad diameter for a given via geometry requires full-wave EM modeling, not a rule of thumb.

Ground Via Placement

At millimeter-wave frequencies, ground via spacing along a microstrip trace must be held below λ/4 at the operating frequency to suppress surface wave modes. Ground via rows flanking critical RF traces are the standard routing practice for Rogers circuit boards operating above 20GHz.

Ground vias also serve as the return current path for vertical transitions—each signal via requires adjacent ground vias at close spacing to minimize the loop area of the return current path through the board. Loop area directly contributes to excess inductance that degrades the via transition performance.

Antenna Feed Design on Rogers RO3003

The antenna feed network—the transmission line connecting the RF source output to the radiating elements—is where most of the insertion loss budget is consumed. Every 0.1 dB of unnecessary feed loss is 0.1 dB less transmit power or receive sensitivity.

Minimizing Feed Line Length

The first design decision: minimize the physical length of the RF path from source to antenna aperture. At millimeter-wave frequencies, substrate loss accumulates rapidly with trace length. A feed network that is several inches long adds meaningful insertion loss before conductor loss or connector losses are even counted. Every millimeter of feed line length matters.

For series-fed patch arrays with corporate feed networks, place the RF source as close to the center of the array as possible to equalize and minimize the individual element feed lengths.

Matched Path Lengths for Phased Arrays

RO3003's Dk 3.00 ± 0.04 enables the phase coherence that phased-array steering requires. But if feed paths of different lengths reach individual array elements, the extra delay in longer paths creates a frequency-dependent phase offset that limits steering accuracy.

For corporate-feed array designs, equal electrical length paths to all elements is the baseline requirement. Equal electrical length means equal physical length times equal Dk—which is only predictable with RO3003's tight Dk tolerance. This is a key reason why mmWave phased-array systems select Rogers RO3003 over lower-cost PTFE alternatives with wider Dk tolerances.

Power Divider and Splitter Topology

Wilkinson dividers are the standard choice for equal-power distribution to array elements: excellent isolation between output ports, low insertion loss, and a compact footprint on 10 mil RO3003. The quarter-wave sections require precise trace width control—exactly the ±5% impedance capability that LDI etching provides.

Rat-race couplers for 180° phase-splitting applications require λ/2 ring circumference, which becomes compact at mmWave frequencies. The tight dimensional tolerance on the ring makes LDI critical; phototool-imaged rings show measurable port imbalance at high frequencies due to cumulative dimensional errors.

Thermal Design Integration with Rogers Circuit Board Layout

RO3003 is a thermal insulator—0.50 W/m/K. Every watt dissipated by an RF transceiver IC beneath a phased-array feed network has to be extracted vertically through copper via structures, not laterally through the substrate.

POFV Array Design Rules

For an RFIC thermal pad, the POFV array geometry determines the effective thermal resistance:

- Array coverage: ≥50% of thermal pad area

- Via diameter: 0.3mm drilled, 0.25mm after plating

- Via pitch: 0.6mm center-to-center

- Fill material: Thermally conductive epoxy, fully filled

- POFV cap plating planarity: Within ±10 μm of surrounding copper

For a typical 3×3mm transceiver thermal pad with a 3×3 array of 0.3mm vias, the effective thermal resistance through the substrate is approximately 15–25°C/W depending on chassis attachment. The detailed thermal modeling and POFV design mechanics are covered in the RO3003 PCB manufacturing thermal management guide.

Copper Pour Strategy for Ground and Thermal Layers

Copper pour on the ground reference plane beneath RF components serves two functions simultaneously: electromagnetic reference plane continuity and lateral heat spreading to the board edge or thermal via array. The pour strategy must be consistent with the hybrid stackup copper density requirements (≥75% on FR-4 inner layers for bow/twist management) while also maintaining RF ground plane integrity.

Avoid copper islands—regions of copper ground pour not connected to the main ground network by multiple vias. Floating copper at high frequencies can resonate, creating spurious radiation that degrades system performance and can appear as interference or ghost signals in sensitive RF receivers.

Translating EM Simulation to Fabrication-Ready Gerbers

Simulation to Layout Handoff Checklist

Before generating final Gerbers from a Rogers circuit board layout:

- All RF trace widths verified against fabrication-measured Dk and core thickness (not simulation nominal)

- Via models in simulation match actual via geometry (diameter, length, anti-pad dimensions)

- Stub elimination method (backdrilling or blind vias) specified in fabrication notes

- POFV arrays marked in Gerbers with fill specification

- Ground via spacing along RF traces verified against λ/4 limit at operating frequency

- TDR coupon placement confirmed on panel layout

- Surface finish specified on all layers (ImAg for RF outer layers)

- Controlled impedance structures listed with targets, tolerances, and layer stack reference

DFM Review: The Last Check Before Fabrication

A well-structured DFM review from a Rogers-qualified fabricator will catch the issues that translate into first-spin hardware failures: via aspect ratios that exceed IPC Class 3 plating limits, copper density on FR-4 inner layers below the hybrid bow/twist threshold, and trace widths that don't match the impedance target given the specified core thickness.

The RO3003 custom PCB engineering guide covers the complete DFM checklist for hybrid stackup designs—including the pre-Gerber and post-Gerber review stages that compress the prototype iteration cycle.

When working with a new supplier for the first time, the RO3003 PCB manufacturer qualification criteria—including plasma capability verification, LDI process capability data, and microsection documentation—are the relevant performance benchmarks before committing an RF design to their process.

From First Hardware to Production

A Rogers circuit board design that performs to simulation on first prototype is the result of three things working in concert: accurate stackup modeling, simulation-verified trace and via geometry, and a fabricator whose measured process parameters match the simulation inputs.

The gap between prototype hardware and simulated performance is almost always traceable to a known root cause. APTPCB's engineering team provides post-prototype analysis support for mmWave programs—TDR data, microsection reports, and process parameter records are available from every batch to correlate measured hardware behavior with fabrication variables.

Submit your Rogers circuit board layout to APTPCB for DFM review before your first prototype run, or contact our RF engineering team to discuss stackup configuration and simulation model alignment for your program.

References

- Dk, Df, and frequency-dependent permittivity data from Rogers Corporation RO3000® Series Circuit Materials Datasheet (Rev 11.2023) and Rogers MWI-2000 calculator.

- Conductor loss and surface roughness model per IPC-2141A Design Guide for High-Speed Controlled Impedance Circuit Boards.

- Via transition modeling methodology from APTPCB High-Frequency PTFE Fabrication Control Plan (2026).

- Antenna feed phase coherence requirements per internal phased-array program specifications.